Les bases du CMOS

Les tampon numérique, les portes logiques et les IC logiques

L’un des événements les plus importants de l’histoire de l’électronique numérique a été le développement de la nouvelle technologie IC connue sous le nom de CMOS en 1969.

Les éléments CI numériques CMOS (MOSFET à symétrie complémentaire) présentent des avantages majeurs par rapport aux types TTL.

Ils sont simples et peu coûteux, consomment un courant de repos proche de zéro, ont une impédance d'entrée très élevée, peuvent fonctionner sur une large plage de tensions d'alimentation, ont une excellente immunité au bruit et sont très faciles à utiliser.

En 1972, le CMOS pratique est arrivé sur la scène commerciale sous la forme d’une toute nouvelle famille de circuits intégrés numériques à vitesse moyenne connue sous le nom de série « 4000 ».

Cette nouvelle famille n'était pas aussi rapide que la technologie TTL alors utilisée dans la série rivale « 74 » de circuits intégrés numériques, mais au milieu des années 1980, un nouveau type de CMOS haute vitesse a été développé et introduit en tant que nouveau membre de la famille 74.

Les avantages de ce nouveau

CMOS « rapide » étaient si grands qu'en 1994, il a dépassé le TTL en termes de

popularité au sein de la série 74, faisant finalement du CMOS la plus populaire

de toutes les technologies de circuits intégrés numériques modernes.

Cette dernière section explique les principes de fonctionnement de ces appareils

CMOS des séries 4000 et 74, et décrit les règles d'utilisation de base du CMOS.

LES BASES DU CMOS

L'élément le plus fondamental de toute famille de circuits intégrés numériques est l'inverseur.

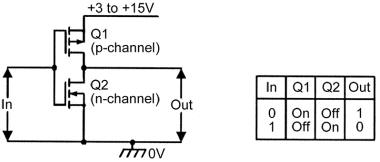

La figure 1 (reprise de la partie 1 de cette série en quatre parties) montre un inverseur CMOS de base.

FIGURE 1. Circuit et table de vérité d'un inverseur CMOS de base

Il s'agit d'un amplificateur de type « totem » composé d'une paire complémentaire de MOSFET à mode d'amélioration câblés en série entre les deux lignes d'alimentation, avec un MOSFET Q1 à canal P en haut et un MOSFET Q2 à canal N en dessous et avec les portes MOSFET (qui ont une impédance d'entrée CC presque infinie) reliées ensemble à la borne d'entrée et la sortie prise à la jonction des deux MOSFET.

La paire peut être alimentée à partir de n’importe quelle alimentation comprise entre 3V et 15V.

L'action numérique de base du dispositif à canal N est telle que son chemin drain-source agit comme un interrupteur en circuit ouvert lorsque l'entrée est à 0 logique, ou comme un interrupteur fermé en série avec une résistance de 400Ω lorsque l'entrée est à logique 1.

Le MOSFET à canal P présente l'inverse de ces caractéristiques et agit comme un interrupteur fermé plus une résistance de 400Ω avec une entrée logique 0 et un interrupteur ouvert avec une entrée logique 1.

L'action de base de l'inverseur

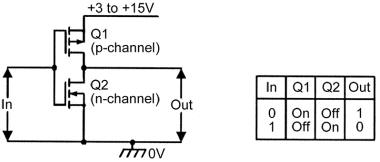

CMOS peut être comprise à l'aide de la figure 2.

FIGURE 2. Circuit

équivalent de l'inverseur numérique CMOS avec (a) entrées logiques 0 et (b)

logiques 1.

La figure 2 (a) montre l'équivalent numérique du circuit inverseur CMOS avec

une entrée logique 0.

Dans cette condition, Q1 (le MOSFET à canal P agit comme un interrupteur fermé en série avec 400Ω, et Q2 agit comme un interrupteur ouvert.

Le circuit ne consomme donc aucun courant de repos mais peut « générer » des courants de commande assez importants dans une charge externe de sortie à la terre via la résistance de sortie de 400Ω (R1) de l'inverseur.

La figure 2 (b) montre le circuit équivalent de l'inverseur avec une entrée logique 1.

Dans ce cas, Q1 agit comme un

interrupteur ouvert, mais Q2 (le MOSFET à canal n) agit comme un interrupteur

fermé en série avec 400Ω ; l'inverseur ne consomme donc aucun courant de repos

dans cette condition, mais peut « absorber » des courants assez importants

provenant d'une charge d'alimentation externe vers la sortie via sa résistance

de sortie interne de 400Ω (R2).

Ainsi, l'inverseur numérique CMOS de base

peut être utilisé avec n'importe quelle alimentation dans la plage de 3V à 15V,

a une impédance d'entrée proche de l'infini, consomme un courant d'alimentation

proche de zéro (généralement 0,01 µA) avec une entrée logique 0 ou logique 1,

peut générer ou absorber des courants de sortie importants et a une impédance de

sortie d'environ 400 W.

Notez que, contrairement à l'inverseur TTL, sa sortie peut osciller de zéro à la valeur entièrement positive du rail d'alimentation, car aucun potentiel n'est perdu via la saturation ou les tensions de jonction polarisées en direct, etc.

Généralement, un basique (style du milieu des années 1970), l'étage CMOS a un délai de propagation allant de 12 ns en utilisant une alimentation 12 V, à 60 nS en 3 V, etc.

LA SÉRIE CI « 4000A »

La gamme initiale de circuits intégrés numériques de 1972 était connue sous le nom de série « 4000A » ; il utilisait le type de base d'inverseur CMOS illustré à la figure 1, mais incorporait de vastes réseaux de « serrage » de diodes et de résistances pour protéger ses MOSFET contre les dommages dus aux charges statiques, etc.

Ainsi, un étage inverseur

complet de la série A a pris la forme de base illustrée à la figure 3.

FIGURE 3. Étage inverseur de base de la série 4000A, avec réseaux de protection

d'entrée et de sortie internes.

Les tests commerciaux de la première gamme de dispositifs CMOS de la série A ont rapidement révélé un certain nombre de problèmes de conception.

Leurs valeurs de résistance marche-arrêt étaient, par exemple, très sensibles aux effets du rayonnement gamma, limitant ainsi leur valeur dans les projets spatiaux, et elles donnaient des impédances de sortie et des délais de propagation inégaux « élevés » et « faibles », etc. ils avaient une mauvaise symétrie de sortie.

Mais le problème le plus

important était que leurs niveaux de commutation de sortie étaient trop

sensibles aux amplitudes de leurs signaux de commutation d'entrée ; la cause

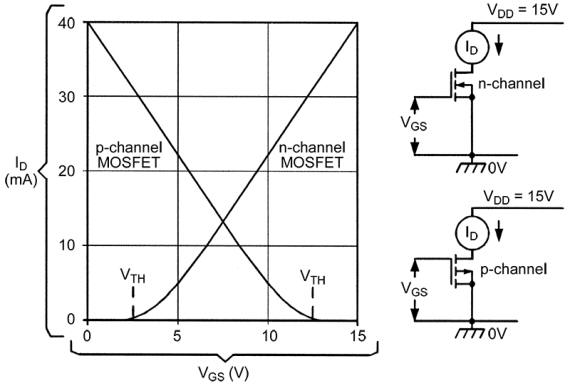

profonde de ce problème peut être comprise à l'aide de la figure 4, qui montre

les caractéristiques linéaires des deux MOSFET de l'inverseur CMOS lorsqu'ils

fonctionnent à partir d'une alimentation de 15 volts.

FIGURE 4.

Caractéristiques typiques de tension de grille/courant de drain des MOSFET à

canaux P et N fonctionnant à partir d'une alimentation de 15 V.

Notez sur la figure 4 que chaque MOSFET agit

comme une résistance contrôlée en tension.

Le dispositif à canal N a une résistance drain-source proche de celle-ci à une tension d'entrée nulle : la résistance reste élevée jusqu'à ce que l'entrée atteigne une valeur de « seuil » d'environ 1,5 à 2,5 volts, mais diminue ensuite à mesure que la tension d'entrée est augmenté, pour finalement tomber à environ 400Ω lorsque l'entrée est égale à la tension de la ligne d'alimentation.

Le MOSFET à canal P présente l'inverse de ces caractéristiques.

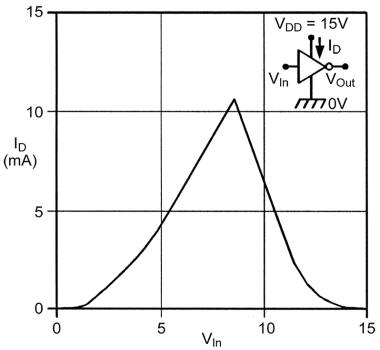

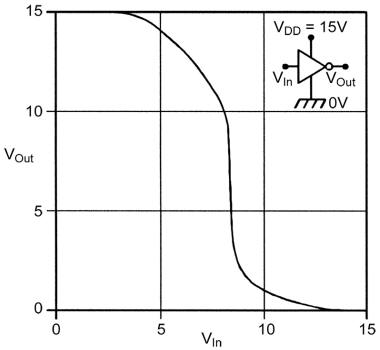

Ainsi, lorsque les deux MOSFET

sont câblés en série et utilisés comme inverseur CMOS de base de 15 volts, ils

produisent le graphique de transfert de courant drain typique illustré à la

figure 5 et le graphique de transfert de tension de la figure 6 ; ces graphiques

peuvent être expliqués comme suit.

FIGURE 5. Caractéristiques typiques de

transfert de courant de drain d'un simple inverseur CMOS.

FIGURE 6. Caractéristiques typiques de transfert de tension d'un simple

inverseur CMOS.

Supposons sur les figures 5 et 6 que la tension d'entrée de l'inverseur CMOS

augmente lentement à partir de zéro.

Le courant de l'inverseur est proche de zéro jusqu'à ce que l'entrée dépasse la tension de seuil du MOSFET à canal N, auquel cas sa résistance commence à chuter et celle du MOSFET à canal P commence à augmenter.

Dans cette condition, le courant de l’inverseur est dicté par la plus grande des deux résistances ; lorsque l'entrée est bien inférieure à la moitié des volts d'alimentation, la résistance du MOSFET à canal N est bien supérieure à celle du dispositif à canal P, donc la sortie est élevée (en logique 1).

Lorsque l'entrée se trouve à une valeur de transition comprise entre 30 et 70 % de la tension d'alimentation, les deux MOSFET ont des valeurs de résistance similaires et l'onduleur agit comme un amplificateur linéaire avec un gain de tension d'environ 30 dB et consomme plusieurs milliampères de courant d'alimentation.

Dans ces conditions, de petits changements de tension d’entrée entraînent des changements importants de tension de sortie.

Lorsque l'entrée augmente encore - bien au-dessus de la moitié des volts d'alimentation - la résistance du MOSFET à canal N tombe en dessous de celle du dispositif à canal P et la sortie devient faible (à 0 logique).

Enfin, lorsque l'entrée dépasse

la valeur seuil du MOSFET à canal P, elle agit comme un interrupteur ouvert et

le courant de l'onduleur retombe près de zéro.

Ainsi, l'onduleur de type

série A fournit une sortie qui commute entièrement entre les valeurs du rail

d'alimentation uniquement si sa tension d'entrée oscille bien au-dessus et en

dessous de ses deux valeurs de tension de seuil internes.

Notez (à partir de la figure 5) que le CMOS tire une brève impulsion de courant d'alimentation à chaque fois qu'il passe par une transition de commutation ; plus le CMOS change d'état dans un temps donné, plus le nombre d'impulsions de courant qu'il prélève sur l'alimentation est grand et plus sa consommation moyenne de courant est grande.

Ainsi, la consommation de courant CMOS est directement proportionnelle à la fréquence de commutation.

LA SÉRIE IC « 4000B »

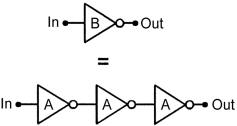

Les défauts de la série 4000A étaient si graves qu'une série CMOS améliorée, connue sous le nom de « 4000B » ou série tamponnée, fut introduite vers 1975, et l'ancienne série 4000A fut progressivement abandonnée.

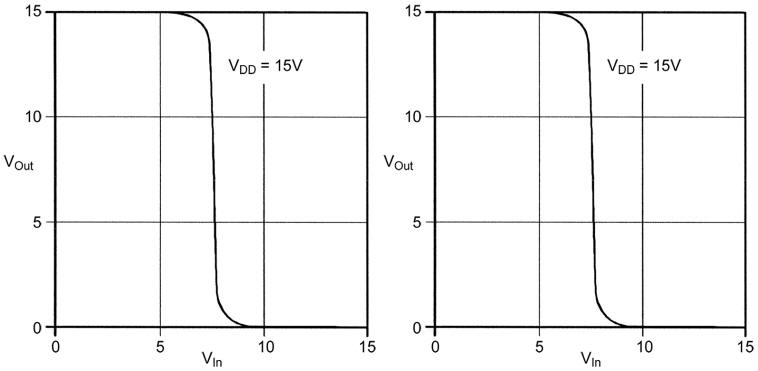

La principale caractéristique

de cette nouvelle série est que chacun de ses « inverseurs » est constitué de

trois inverseurs de base câblés en série, comme le montre la figure 7, de sorte

que chaque inverseur « tamponné » présente un gain de tension linéaire typique

de 70 à 90 dB et a le graphique de transfert de tension typique de la figure 8,

dans lequel toute entrée inférieure à VDD/3 est reconnue comme une entrée

logique 0 et toute entrée supérieure à 2 VDD/3 est reconnue comme une entrée

logique 1.

FIGURE 7. Un inverseur CMOS série B peut être réalisé en

câblant trois types de série A en série.

FIGURE 8. Graphique de transfert de tension de l'onduleur série B de la

figure 7.

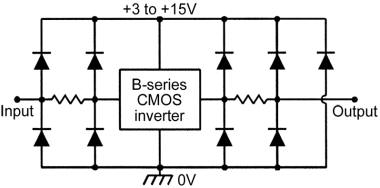

D'autres changements dans la nouvelle série incluent une symétrie de

sortie-drive grandement améliorée et une immunité aux effets du rayonnement

gamma, de nouveaux et meilleurs réseaux de protection d'entrée et de sortie

(voir Figure 9) et des tensions nominales améliorées (généralement jusqu'à 15 V

maximum, mais jusqu'à 18 V maximum en certaines versions du fabricant, contre 12

V maximum dans la série A d'origine).

FIGURE 9. inverseur de base de la

série 4000B avec réseaux de protection d'entrée et de sortie typiques.

L'un des inconvénients de la série B est que ses délais de propagation sont plus importants que ceux de l'ancienne série A.

Pour contrer ce problème,

quelques appareils de nouvelle génération sont produits dans un format « unbuffered »

(désigné par le suffixe « UB »), mais intègrent toutes les autres améliorations

de la série B.

En règle générale, les inverseurs UB ont un gain CA de 23

dB à 10 volts et sont utiles dans plusieurs applications analogiques.

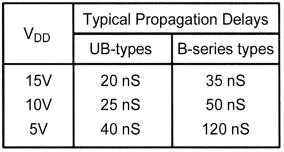

Notez que la bande passante et les délais de propagation d'un dispositif CMOS varient en fonction de la tension d'alimentation et de la charge de sortie capacitive.

La figure 10 répertorie les

délais de propagation typiques des onduleurs des séries UB et B lorsqu'ils sont

utilisés avec des valeurs d'alimentation de 5V, 10V et 15V lors de la commande

d'une charge de 50 pF.

FIGURE 10. Retards de propagation typiques des

onduleurs de la série 4000B lors de la commande d'une charge de 50 pF.

LA SÉRIE « 4500B » DE ICS

La gamme de circuits intégrés de la série 4000B se compose principalement de dispositifs SSI ou MSI assez simples tels que des portes logiques et des compteurs simples, etc.

À la fin des années 1970 et au début des années 1980, un certain nombre de circuits intégrés CMOS MSI et LSI de type B plus complexes, tels que des encodeurs. , décodeurs et compteurs préréglables (etc.) ont été introduits.

Ces dispositifs avancés portent les numéros « 45XX » ou « 47XX » et sont généralement connus sous le nom de série 4500 de circuits intégrés CMOS.

ICS CMOS « RAPIDE »

Au début des années 1980, les ingénieurs se sont efforcés de concevoir un type de CMOS très rapide qui pourrait surclasser le LS TTL lorsqu'il était alimenté par une alimentation de 5 volts et pourrait ainsi devenir la technologie dominante au sein de la série 74 de circuits intégrés.

Le CMOS normal est basé sur la technologie MOSFET (Metal-Oxide Silicon FET), et il s'agit simplement d'une variante de la technologie IGFET (Insulated-Gate FET).

Plus précisément, un dispositif

MOSFET est un dispositif IGFET qui utilise une isolation de grille en oxyde

métallique, et la première grande étape dans le développement d'un CMOS « rapide

» a été d'utiliser une isolation de grille en oxyde de silicium plutôt qu'en

oxyde métallique dans les IGFET de base.

Cette mesure simple a entraîné

une réduction spectaculaire de la capacité d’entrée interne de l’IGFET et une

augmentation tout aussi spectaculaire de la vitesse de fonctionnement.

L'étape suivante consistait à appliquer ces nouveaux IGFET à la configuration CMOS de base.

Lorsque cela a été fait et que des changements importants ont été apportés à la géométrie de l'élément, le dispositif résultant agissait comme un CMOS normal mais était aussi rapide que le LS TTL lorsqu'il fonctionnait à partir d'une alimentation de 5 volts et (contrairement à certaines autres versions de CMOS) avait un excellent pilotage de sortie.

À proprement parler, ce nouveau

dispositif aurait dû recevoir un nom spécial tel que CSOS (Complementary

Silicon-Oxide Silicon FET), mais a simplement été baptisé CMOS « rapide ».

Le CMOS rapide présente de nombreuses similitudes avec le CMOS conventionnel

de la série 4000B.

Il est disponible en versions de base avec tampon (triple inverseurs) et sans tampon (inverseur unique), et toutes les entrées et sorties sont protégées via des réseaux internes de diodes et de résistances.

Il peut (dans la plupart des cas) utiliser n'importe quelle alimentation dans la plage de 2V à 6V et, lors de son introduction, il était destiné à remplacer de nombreux dispositifs existants de la série 74 de circuits intégrés.

Depuis lors, cependant, il a également été utilisé pour créer des versions rapides de nombreux dispositifs populaires des séries de circuits intégrés 4000B et 4500B.

SOUS-FAMILLES CMOS SÉRIE 74

Lorsque la série 74 de circuits intégrés est apparue pour la première fois en 1972, elle était entièrement basée sur la technologie TTL, qui consomme intrinsèquement un courant de repos assez élevé.

À la fin des années 1970, une version légèrement modifiée du CMOS standard (optimisé pour un fonctionnement en 5 V) a été introduite en tant que nouvelle sous-famille « C » au sein de la gamme d'ICs de la série 74 et offrait l'avantage d'une consommation de courant de repos proche de zéro. .

Cette sous-famille C était trop

lente et avait une capacité de sortie trop faible pour obtenir une grande

popularité, mais au cours des années suivantes, le type rapide de CMOS a été

développé spécifiquement pour être utilisé dans la série 74, comme déjà décrit,

et ainsi Jusqu'à présent, un total de cinq sous-familles CMOS ont été

introduites dans la série 74, comme suit :

CMOS standard (C) (maintenant

obsolète).

Il s'agissait d'un CMOS de type MOSFET pratiquement normal au format série 74. En règle générale, une seule porte NAND à deux entrées 74C00 consommait environ 15 mW à 10 MHz et présentait un retard de propagation de 60 nS à 5V.

CMOS haute vitesse (HC).

Introduit au début des années 1980, il s'agit de la version de base rapide en oxyde de silicium du CMOS et offre des performances de vitesse similaires au LS TTL, mais avec des niveaux de consommation d'énergie CMOS.

Les appareils de la série HC 74 utilisant cette technologie disposent d'entrées compatibles CMOS. En règle générale, une seule porte NAND à deux entrées 74HC00 consomme moins de 1 µA de courant de repos et présente un retard de propagation de 8 nS à 5V.

CMOS haute vitesse (HCT).

Ce sont des appareils rapides de type HC, mais dotés d'entrées compatibles TTL et destinés à être pilotés directement à partir des sorties TTL. En règle générale, une porte NAND à deux entrées 74HCT00 consomme moins de 1 µA de courant de repos et présente un délai de propagation de 18 nS.

CMOS avancé haute vitesse (AC).

À la fin des années 1980, de nouveaux progrès dans les techniques de conception et de fabrication de CMOS haute vitesse ont permis d'obtenir des performances de vitesse encore meilleures.

Les appareils de la série AC 74 utilisant cette technologie disposent d'entrées compatibles CMOS.

Généralement, une porte NAND à deux entrées 74AC00 a un délai de propagation de 5 nS.

CMOS avancé haute vitesse (ACT).

Il s'agit d'appareils de type AC, mais dotés d'entrées compatibles TTL et destinés à être pilotés à partir de sorties TTL. Généralement, une porte NAND à deux entrées 74ACT00 a un délai de propagation de 7 nS.

VARIATIONS DE BASE DU CIRCUIT CMOS

Il existe trois variantes importantes du circuit CMOS de base qui sont souvent utilisées dans les circuits intégrés de la série 4000B à vitesse moyenne et des gammes de dispositifs rapides de la série 74.

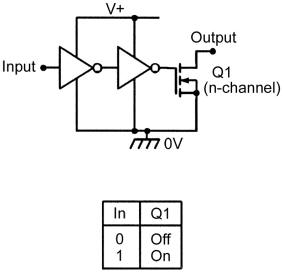

La première d’entre elles est la configuration « open drain », utilisée dans certains inverseurs et tampons, etc.

La figure 11 montre un

inverseur à drain ouvert typique, qui est configuré comme un inverseur CMOS

normal à trois étages à gain élevé, sauf que l'étage final est constitué d'un

seul IGFET à mode à canal N (Q1) dont le drain est connecté directement. à la

borne de sortie du circuit.

FIGURE 11. Onduleur CMOS de base avec sortie

à drain ouvert.

L'action du circuit est telle que Q1 est coupé lorsque l'entrée est à 0

logique et est activé lorsque l'entrée est à 1 logique.

Le circuit peut être utilisé

pour piloter directement une charge externe connectée entre « OUT » et le rail

d'alimentation + ve, auquel cas la charge s'active lorsqu'une entrée logique 1

est appliquée.

La deuxième variante concerne l'utilisation d'une sortie

de type « à trois états » qui, en utilisation normale, donne une sortie logique

0 ou logique 1 à faible impédance conventionnelle, mais peut également être

réglée sur un troisième état dans lequel la sortie est effectivement un circuit

ouvert.

Cette fonctionnalité est utile

pour permettre à plusieurs sorties ou entrées d'être câblées à un bus commun et

de communiquer le long de ce bus en ACTIVANT une seule sortie et un seul

périphérique d'entrée à la fois.

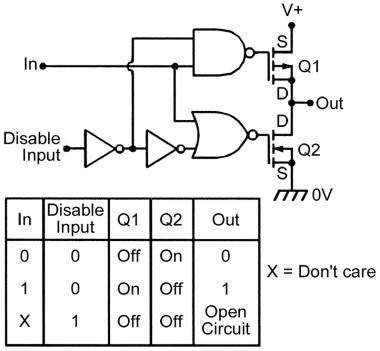

La figure 12 montre le circuit typique

d'un tampon non inverseur de ce type, ainsi que sa table de vérité.

FIGURE 12. Circuit de base d'un tampon non inverseur CMOS à trois états.

Ainsi, lorsque la commande DISABLE INPUT est au niveau logique 0, le circuit donne un fonctionnement normal en « tampon » ; dans cette condition, Q1 est désactivé et Q2 est activé lorsque IN est à 0 logique, conduisant ainsi OUT à 0 logique.

L’inverse de cette action est obtenu lorsque l’entrée est au niveau logique 1.

Lorsque la commande DISABLE INPUT est réglée sur logique 1, Q1 et Q2 sont désactivés, quel que soit l'état de l'entrée IN, et dans cette condition, OUT est effectivement désactivée et agit comme un circuit ouvert.

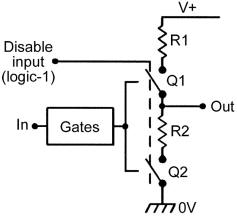

La figure 13 montre le circuit

équivalent simplifié de ce tampon lorsqu'il est dans son état de sortie haute

impédance.

FIGURE 13. Équivalent d'un circuit tampon à trois états dans

son troisième état à haute impédance.

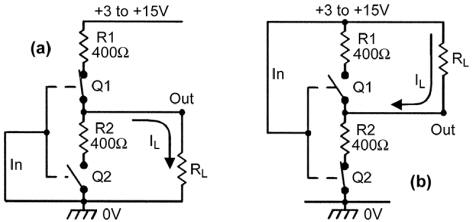

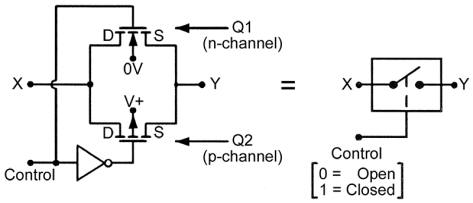

La troisième variante du circuit CMOS est celle du « commutateur bilatéral »

ou porte de transmission.

L'action de base de tout IGFET en mode amélioration est telle que son chemin drain-source agit comme un commutateur unidirectionnel presque parfait :

Lorsque l'IGFET est désactivé, le chemin agit comme un circuit ouvert, et lorsqu'il est activé, il agit comme une résistance de faible valeur et (contrairement à un transistor bipolaire) ne souffre pas de problèmes de tension de saturation, etc.

Lorsqu'il est allumé, un IGFET à canal N fait passer le courant du drain à la source, et un IGFET à canal P laisse passer le courant de la source au drain.

Ainsi, un commutateur

électronique bidirectionnel ou bilatéral presque parfait peut être réalisé en

câblant un IGFET à canal N et un IGFET à canal P en parallèle (source à source

et drain à drain) et en pilotant leurs grilles en antiphase, comme le montre la

figure 14.

FIGURE 14. Commutateur bilatéral ou porte de transmission CMOS

de base.

Ici, les deux chemins IGFET sont effectivement ouverts lorsque l'entrée

CONTROL est à 0 logique et fermés lorsque l'entrée CONTROL est à 1 logique.

En condition fermée, le courant peut circuler de X à Y via Q1, ou de Y à X via Q2 ; le courant peut ainsi circuler dans les deux sens entre ces points, et le circuit simule ainsi un simple interrupteur électromécanique.

RÈGLES D'UTILISATION DE BASE DU CMOS

Les circuits intégrés CMOS sont très faciles à utiliser.

Ils sont très tolérants aux variations de tension d'alimentation et, contrairement aux types TTL, présentent très peu de problèmes de correspondance entrée-drive / sortie-drive.

Il n'y a, en fait, que sept thèmes d'utilisation de base à prendre en compte lorsqu'on traite du CMOS, à savoir :

Sélection du type ; Manipulation du CMOS ; Alimentations électriques ; Signaux d'entrée ; Entrées inutilisées ; et Interfaçage.

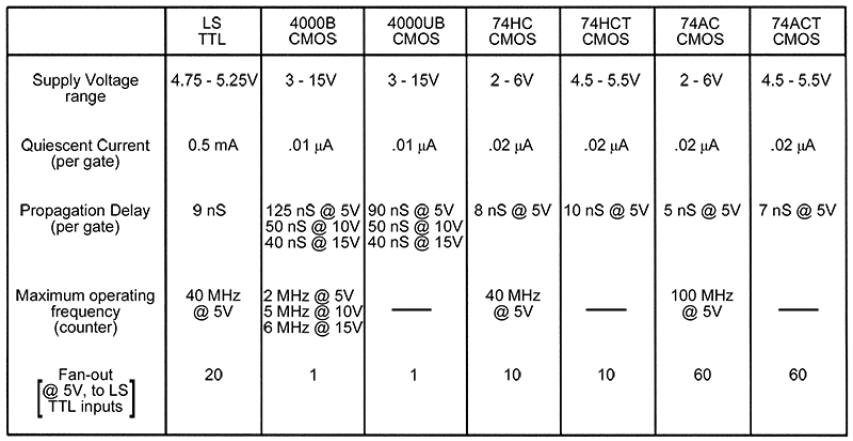

Sélection du type

La question « Quelle famille CMOS dois-je utiliser ? »

Il est facile de répondre à cette question à l'aide de la figure 15, qui répertorie les principales caractéristiques des six sous-familles CMOS modernes facilement disponibles et les compare à celles du LS TTL.

FIGURE 15. Tableau montrant les caractéristiques générales du LS TTL et des six principaux types de circuits intégrés numériques CMOS.

Parmi ces types, la sous-famille 4000UB n'est disponible que sous la forme de quelques circuits intégrés tampons et inverseurs simples, et doit être considérée comme une simple variante de la sous-famille principale 4000B.

Les types 74HCT et 74ACT sont

destinés à être directement pilotés à partir des sorties TTL et ne sont utilisés

que dans quelques applications spécialisées.

Parmi les trois

sous-familles CMOS restantes (4000B, 74HC et 74AC), la sous-famille 4000B peut

être utilisée dans toute application nécessitant l'utilisation d'une

alimentation comprise entre 3 V et 15 V et dans laquelle les fréquences de

fonctionnement maximales ne dépasse pas 2 MHz à 5 V ou 6 MHz à 15 V.

Alternativement, si les

tensions d'alimentation sont limitées à la plage de 2 V à 6 V, la sous-famille

74HC peut être utilisée pour fonctionner à des fréquences allant jusqu'à 40 MHz

à 5 V, ou la sous-famille 74AC à des fréquences allant jusqu'à 100 MHz à 5 V.

Notez que tous les circuits intégrés TTL ont des exigences particulières en

matière de pilotage d'entrée, et les numéros de sortance de la figure 15

montrent combien d'entrées LS TTL standard connectées en parallèle peuvent être

directement pilotées à partir de la sortie de chaque membre de la sous-famille

répertorié.

Ainsi, le 4000B CMOS ne peut

piloter qu'une seule de ces entrées, mais les 74HC et HCT CMOS peuvent chacun

piloter 10 de ces entrées, et les 74AC et ACT peuvent chacun piloter jusqu'à 60

entrées LS TTL.

Manipulation du CMOS

Le CMOS est basé sur la technologie IGFET à haute impédance qui, lorsqu'elle est manipulée, est facilement endommagée par des charges statiques à haute tension du type de celles qui peuvent s'accumuler sur le corps de la personne qui les manipule.

Tous les circuits intégrés

numériques CMOS modernes intègrent un vaste circuit interne de serrage de diode

conçu pour protéger leurs IGFET internes contre les dommages causés par des

quantités raisonnables de ce type de décharge statique lorsque le circuit

intégré est manipulé.

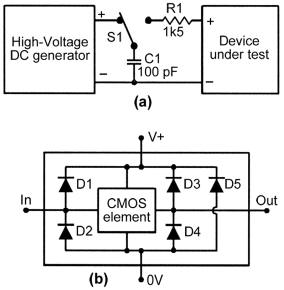

La figure 16(a) montre le circuit de laboratoire de

base utilisé — lors du test des circuits intégrés CMOS — pour simuler des

valeurs raisonnables de décharge statique d'un corps humain ; C1 a une valeur de

100 pF et simule la capacité corporelle typique d'un adulte humain chargé, et R1

a une valeur de 1,5K et simule la résistance de décharge typique du corps.

FIGURE 16. (a) Circuit de test de décharge électrostatique typique et (b) équivalent simple d'un élément IC numérique CMOS.

Lorsqu'un CI CMOS est soumis à des tests d'évaluation, C1 est chargé à une tension de test de haute valeur via S1, puis appliqué à deux des points de test du CI via S1 et R1.

Un élément CMOS de base possède quatre bornes (IN, OUT, V+ et 0V) et dispose donc d'un total de 12 permutations de test possibles à deux broches. Le circuit de test est appliqué à chacune de ces permutations à deux broches dans une séquence de test complète.

En règle générale, les circuits intégrés numériques CMOS modernes devraient survivre à une tension de test de 2,5 kV dans tous ces modes de test.

La figure 16 (b) montre la forme de base du circuit de protection interne d'un élément CMOS.

Ici, D1 ou D2 sont conducteurs si IN essaie de dépasser V+ ou de descendre en dessous de 0 V ; D3 ou D4 fonctionnent si OUT essaie de dépasser V+ ou de descendre en dessous de 0 V.

D5 est conducteur si 0V tente

de dépasser V+ ; D5 conduit également en mode Zener si V+ passe de plus

d'environ 20 V au-dessus de 0 V.

Il est important de comprendre la

signification de ces tests CMOS de protection contre les décharges statiques.

Supposons qu'une tension de test de 3 kV soit appliquée entre les broches 0V et V+ connectées en inverse du circuit intégré. Dans cette condition, D5 est polarisé en direct et C1 se décharge via D5 et R1 ; R1 limite le courant de décharge de crête de C1 à 2 A et lui donne une constante de temps de base de 150 nS.

Ainsi, D5 ne laisse passer qu’un très bref pic de courant direct lorsque C1 se décharge.

Si la constante de temps thermique de D1 est très longue par rapport à la période du pic, il ne risque pas de subir de dommages dus à ce test, même s'il ne peut gérer que des courants continus normaux de (disons) 25 mA maximum.

Notez que la tension de

crête apparaissant aux bornes de D5 dans ce test est d'environ 1V ; la majeure

partie de la tension de décharge de 3 kV de C1 est perdue aux bornes de R1.

Les réseaux de protection utilisés dans les circuits intégrés CMOS ne sont

pas conçus pour être efficaces contre des valeurs massives de décharges

statiques, telles que les plusieurs milliers de volts pouvant être générés par

une personne se pavanant vigoureusement sur un tapis en nylon, etc.

Par conséquent, lors de la manipulation de circuits intégrés CMOS nus , prenez toujours des précautions raisonnables contre l'accumulation de charges statiques importantes.

Ne portez pas de vêtements en

nylon et n'utilisez pas de tapis en nylon dans l'atelier et assurez-vous que les

fers à souder, etc., sont correctement mis à la terre.

Pour être vraiment

en sécurité, portez un bracelet métallique mis à la terre lorsque vous

travaillez avec du CMOS, en particulier lors du soudage.

Notez cependant qu'en réalité,

il est très peu probable que vous endommagiez un circuit intégré CMOS lors d'une

manipulation normale, même si vous ne pas porter de bracelet mis à la terre.

Alimentations

Les circuits intégrés CMOS des types 4000B, 74HC et 74AC sont conçus pour fonctionner sur une large plage de tensions d'alimentation et peuvent donc être alimentés par des piles ou par des alimentations régulées ou non régulées.

Cependant, les types 74HCT et

74ACT sont conçus pour fonctionner à partir d'alimentations comprises entre 4,5

V et 5,5 V et doivent être alimentés à partir d'alimentations à faible impédance

et bien régulées.

Tous les circuits intégrés CMOS génèrent des fronts de

commutation d'impulsions rapides.

Par conséquent, la plupart des circuits CMOS doivent être utilisés avec un PCB conçu pour offrir un excellent découplage de l'alimentation haute fréquence à chaque circuit intégré.

D'une manière générale, les pistes d'alimentation et de masse du PCB doivent être les plus larges possibles (idéalement, la piste 0V doit prendre la forme d'un plan de masse), toutes les connexions et interconnexions doivent être aussi courtes et aussi directes que possible, les pistes du PCB doivent aussi être courtes et aussi directes que possible.

Les rails d'alimentation

doivent être généreusement saupoudrés de condensateurs électrolytiques au

tantale de 4,7 µF (au moins un pour 10 CI) pour améliorer le découplage, et avec

des disques céramiques de 10 nF (au moins un sur quatre CI, placés aussi près

que possible entre les broches d'alimentation d'un CI) pour améliorer le

découplage.

Lorsque vous expérimentez avec des circuits intégrés CMOS, ne

laissez jamais l'alimentation être connectée dans la mauvaise polarité, car cela

entraînerait le passage de courants d'alimentation importants à travers les

réseaux de diodes de protection du circuit intégré (en particulier via D5 dans

la figure 16) et causerait des dommages instantanés au circuit intégré.

Signaux d'entrée

Lors de l'utilisation du CMOS, tous les signaux d'entrée du CI doivent - à moins que le CI ne soit équipé d'une entrée de type Schmitt - avoir des fronts montants et descendants très nets.

Si les temps de montée ou de descente sont trop longs, ils peuvent permettre à la borne d'entrée de planer dans la zone linéaire de l'élément CMOS suffisamment longtemps pour que l'élément éclate en oscillations sauvages et génère des signaux de sortie spasmodiques susceptibles de perturber les circuits associés (tels que les compteurs et les registres, etc).

Si nécessaire, les signaux

d'entrée lents peuvent être convertis en signaux rapides en les transmettant à

la borne d'entrée du circuit intégré via des éléments CMOS Schmitt.

Une

façon possible d'endommager le CMOS consiste à utiliser un signal d'entrée ou de

sortie à très faible impédance qui est soit connecté au CMOS lorsque son

alimentation est coupée, soit d'une amplitude si grande qu'il force la borne

d'entrée bien au-dessus de la ligne d'alimentation positive ou sous le rail zéro

volt, provoquant ainsi le passage d'un courant dommageable à travers une ou

plusieurs diodes de protection du circuit intégré (en particulier, à travers les

diodes d'entrée D1 ou D2 de la figure 16, ou les diodes de sortie D3 ou D4).

La possibilité de tels dommages

peut être éliminée en câblant une résistance 1K en série avec chaque borne

d'entrée/sortie pour limiter ces courants à des valeurs sûres de quelques

milliampères.

Entrées inutilisées

Les bornes d'entrée CMOS inutilisées ne doivent jamais être laissées simplement tomber, mais doivent toujours être liées à des niveaux logiques définis en les connectant directement aux rails d'alimentation ou de masse (en fonction des exigences logiques du circuit intégré), ou à un autre point bien défini aux niveaux logiques nécessaires.

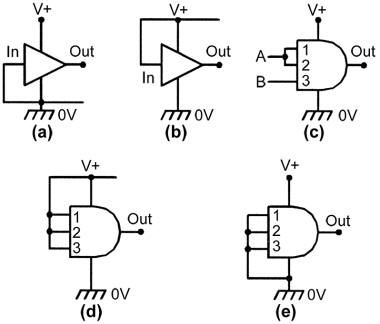

La figure 17 montre certaines

des options disponibles.

FIGURE 17. Autres méthodes de connexion des

entrées CMOS indésirables (voir texte).

Si l'entrée non utilisée se trouve sur une porte à entrées multiples, elle

peut être désactivée en la court-circuitant à l'une des entrées utilisées de la

porte, comme dans la figure 17(c), où une porte ET à trois entrées est utilisée

comme une porte à deux entrées.

Si le CI est un type à

portes multiples dans lequel une porte entière n'est pas utilisée, la porte doit

être désactivée en liant toutes ses entrées à un point haut ou bas commun, comme

en (d) et (e).

Toutes les bornes d'entrée CMOS utilisées doivent

également être liées à des niveaux logiques définis et ne doivent jamais être

autorisées à flotter.

La figure 18 montre trois

options couramment utilisées.

FIGURE 18. Toutes les entrées CMOS

utilisées doivent être liées à des niveaux logiques définis.

Dans (a), l’entrée est normalement liée au niveau bas par R1, et dans (b)

elle est normalement liée au niveau haut par R1.

Dans (c), l'entrée est couplée

directement à la sortie d'un étage de pilotage, qui détermine le niveau logique

d'entrée.

Interfaçage

Un circuit d’interface est un circuit qui permet à un type de système d’être connecté de manière judicieuse à un autre type de système.

Dans un système purement CMOS,

dans lequel tous les circuits intégrés sont conçus pour se connecter directement

entre eux, des circuits d'interface sont généralement nécessaires uniquement aux

points d'entrées initiaux et de sorties finaux du système, pour leur permettre

de fusionner avec le monde extérieur via des éléments tels que des commutateurs,

des capteurs, relais et indicateurs, etc.

Parfois, cependant, les

circuits intégrés CMOS peuvent être utilisés conjointement avec d'autres

familles logiques (telles que TTL), auquel cas une interface peut être

nécessaire entre les différentes familles.

Ainsi, en ce qui concerne le CMOS, il existe trois classes de base de circuits d'interface, à savoir :

l'interfaçage d'entrée,

l'interfaçage de sortie et l'interfaçage de la famille logique.

Interface d'entrée

Les signaux numériques arrivant aux entrées d'un système CMOS doivent être propres, avec des niveaux logiques bien définis et des temps de montée et de descente rapides. Il incombe aux circuits d’interface d’entrée de convertir les signaux d’entrée externes dans ce format.

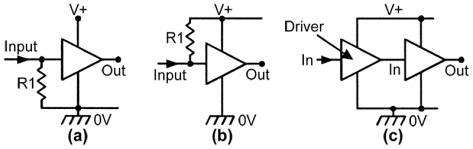

Les figures 19 à 22 montrent quatre exemples simples d'un tel circuit mais doivent utiliser des éléments CMOS Schmitt et peuvent utiliser n'importe quelle tension de rail d'alimentation positive dans les limites de fonctionnement de l'élément CMOS.

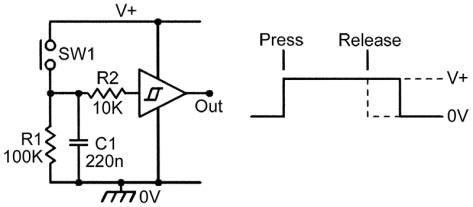

Le circuit de la figure 19 est conçu pour nettoyer les signaux de commutation sales du commutateur à bouton-poussoir SW1 et les convertir en une forme appropriée pour piloter une entrée CMOS normale. Ici, l'entrée du tampon Schmitt est liée à la masse via R1 et R2 et est normalement faible.

FIGURE 19. Bouton-poussoir silencieux CMOS.

Lorsque SW1 est fermé, C1 se charge rapidement et fait monter la sortie Schmitt, mais lorsque SW1 s'ouvre à nouveau, C1 se décharge relativement lentement via R1, et la sortie Schmitt ne redevient basse qu'environ 20 mS plus tard.

Le circuit ignore ainsi les

effets de commutation transitoires du bruit SW1 et du rebond de contact, etc.,

et génère une forme d'onde de commutation de sortie propre avec une période qui

est environ 20 mS plus longue que la durée moyenne de fermeture du commutateur

SW1.

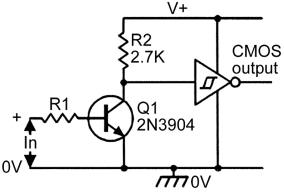

La figure 20 montre un circuit qui peut être utilisé pour interfacer

presque n'importe quel signal numérique propre à une entrée CMOS normale.

FIGURE 20. Interface d'entrée du transistor CMOS.

Ici, lorsque le signal d'entrée est inférieur à 500 mV (tension d'activation minimale de Q1), Q1 est coupé et la sortie de Schmitt inverseur est à 0 logique. Lorsque l'entrée est nettement supérieure à 600 mV, Q1 est activé et la sortie Schmitt passe au logique 1.

Notez que le signal d'entrée

numérique peut avoir n'importe quelle valeur de tension maximale et que R1 est

choisi pour simplement limiter le courant de base de Q1 à une valeur sûre.

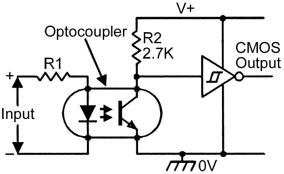

La figure 21 est une simple variante du circuit ci-dessus, avec le

transistor intégré dans un optocoupleur ; l'action du circuit est telle que la

sortie de Schmitt est au niveau logique 0 lorsque l'entrée de l'optocoupleur est

nulle, et au niveau logique 1 lorsque l'entrée est haute ; notez que

l'optocoupleur fournit une isolation électrique totale entre les signaux

d'entrée et CMOS.

FIGURE 21. Interface d'entrée de l'optocoupleur CMOS.

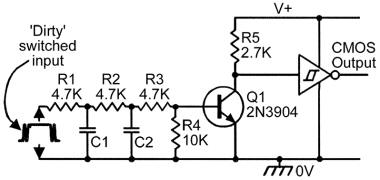

Enfin, la figure 22 est une autre variante de circuit simple, avec le signal

d'entrée numérique de base envoyé à la base de Q1 via le réseau de filtres

passe-bas R1-C1-R2-C2, qui élimine les composants haute fréquence indésirables

et peut ainsi convertir des signaux d'entrée très sales (comme ceux des

disjoncteurs de véhicules, etc.) dans un format CMOS propre.

FIGURE 22.

Interface d'entrée à commutation sale CMOS.

Interface de sortie

Les étages de sortie totem-pole CMOS sont conçus pour générer ou absorber des valeurs de crête assez élevées du courant de sortie.

Par conséquent, si la sortie est directement court-circuitée au rail d'alimentation zéro volt ou positif du circuit intégré, les courants de sortie CC résultants peuvent, dans certains cas, être si élevés que le circuit intégré peut être endommagé.

Ainsi, lorsqu'un CI CMOS est

utilisé pour piloter une charge CC, son courant de charge doit toujours être

limité à une valeur sûre.

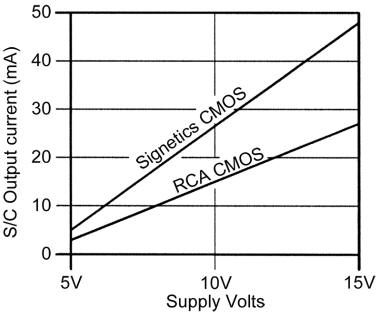

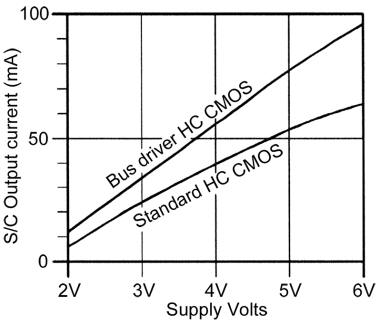

La figure 23 montre les courants de sortie de

court-circuit typiques de deux étages de sortie CMOS série 4000B de fabricants

différents sur la plage de tension de fonctionnement de 5 V à 15 V.

FIGURE 23. Courants de sortie de court-circuit typiques de la série 4000B (à 25 OC).

En pratique, les valeurs DC

maximales de ces charges de sortie doivent être limitées à 10 mA de courant ou

100 mW de puissance dissipée, la valeur la plus basse étant retenue.

La

figure 24 montre les courants de sortie de court-circuit typiques des versions

standard et de pilote de bus des étages de sortie CMOS série 74HC sur la plage

de tension de fonctionnement de 2 V à 6 V.

FIGURE 24. Courants de sortie de court-circuit typiques de la série 74HC (à 25 OC).

En pratique, les valeurs DC

maximales de ces courants doivent être limitées à 25 mA dans les types HC

standards et à 35 mA dans les types HC driver de bus.

Le seul cas où

cette question de limitation de courant est susceptible de présenter un réel

problème est lors de l'utilisation de CMOS pour piloter un certain type de

charge de LED (y compris celles aux entrées des optocoupleurs, etc.).

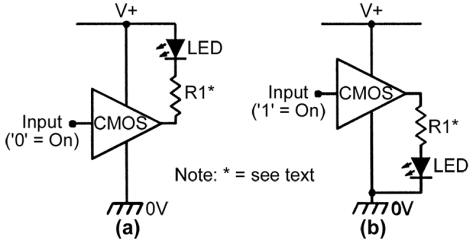

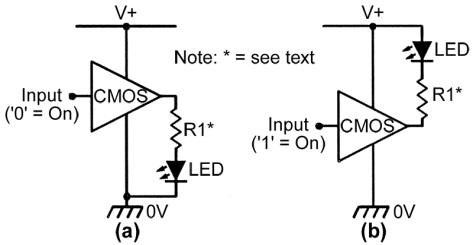

Les figures 25 et 26 montrent

des méthodes de base pour piloter une LED via des éléments CMOS non inverseurs

ou inverseurs.

FIGURE 25. Interface de sortie de pilotage de LED,

utilisant des éléments CMOS non inverseurs.

FIGURE 26. Interface de sortie de pilotage de LED, utilisant des éléments CMOS inverseurs.

Notez dans ces circuits que R1

règle le courant ON de la LED et a une valeur de [(V+ - Vs)/I] -Rx, où V+ est la

tension d'alimentation, Vs est la tension de saturation de la LED (généralement

2,0 à 2,5 volts), I est le courant ON de la LED (en ampères) et Rx est la

résistance à la saturation des éléments CMOS (et varie considérablement en

fonction de la tension, du courant et des circuits intégrés individuels).

Cependant, en règle générale, Vs est égal à 2,2 V et Rx a une valeur

approximative de 100 Ω dans une sortie standard de 74HC ou de 70 Ω dans une

sortie de pilote de bus, ou de 500 Ω dans une sortie standard de 4 000B.

Ainsi, pour régler le courant

LED à 10 mA, R1 a besoin d'une valeur d'environ 180 Ω dans un circuit 74HC

standard 5 V, 220 Ω dans un circuit pilote de bus 5 V 74HC, 270 Ω dans un

circuit 10 V 4000B ou 820 Ω dans un circuit 15 V 4000B.

Notez que les

sorties CMOS peuvent être utilisées pour piloter n'importe lequel des circuits

d'interface de sortie TTL de base illustrés dans les figures 12 à 17 (voir

Interfaçage) de cette série en câblant

simplement une résistance de limitation de courant en série avec la sortie CMOS,

pour limiter son courant de sortie à une valeur sûre.

Interfaçage de

la famille logique

Il est généralement déconseillé de mélanger différentes familles logiques dans n'importe quel système, mais dans les cas où cela se produit, le mélange est généralement effectué entre des périphériques TTL et CMOS.

Notez que les types 74HCT et 74ACT de circuits intégrés CMOS sont conçus pour être directement pilotés à partir des sorties TTL, sans nécessiter de méthodes d'interface spéciales.

Notez également que les

éléments CMOS standard des séries 4000B et 74CXX ont des sorties très faibles et

ne peuvent piloter qu'un seul élément TTL ou LS TTL standard, mais les éléments

CMOS des séries 74HCXX (et 74ACXX) ont d'excellentes sorties et peut piloter

directement jusqu'à deux entrées TTL standard, ou 10 entrées LS TTL, ou 20

entrées ALS TTL.

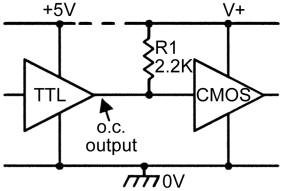

La plupart des circuits intégrés TTL avec sorties à

collecteur ouvert (OC) ont une tension de sortie nominale d'au moins 15 V (mais

le circuit intégré principal a une valeur nominale normale de 5 V) et peuvent

être interfacés à l'entrée d'un circuit intégré logique CMOS en utilisant les

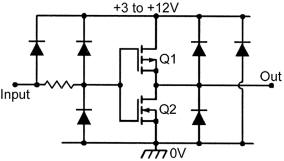

connexions indiquées dans la figure 27.

FIGURE 27. TTL (sortie à

collecteur ouvert) vers interface CMOS, utilisant des rails +ve communs ou

indépendants.

Ici, R1 agit comme une résistance de rappel, et le circuit intégré CMOS peut

soit partager l'alimentation 5 V du circuit intégré TTL, soit utiliser son

propre rail d'alimentation positif de 5 V à 15 V.

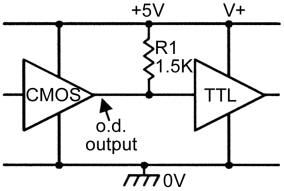

De même, un CI CMOS avec une

sortie à drain ouvert (OD) peut être interfacé à une entrée TTL normale en

utilisant les connexions illustrées dans la figure 28 mais, dans ce cas, les

deux CI doivent partager un rail d'alimentation 5 V commun.

FIGURE 28.

CMOS (sortie à drain ouvert) vers interface TTL.

NOTATIONS SUR LES BROCHES D'ALIMENTATION CMOS

La plupart des circuits intégrés numériques n'ont que deux broches d'alimentation, dont l'une se connecte au rail d'alimentation positif d'un circuit et l'autre au rail zéro volt.

Dans les circuits intégrés TTL, ces broches sont classiquement notées respectivement VCC et GND, la notation VCC impliquant que le rail positif se connecte généralement aux côtés collecteur des transistors internes du circuit intégré.

Lorsque les circuits intégrés CMOS de la série 4000 ont été introduits pour la première fois, les broches d'alimentation ont été renommées respectivement VDD et VSS, ce qui implique que le rail positif se connecte généralement au côté drain des IGFET internes du circuit intégré, et le rail zéro volt aux côtés source.

Ces notations sont en fait

assez ambigües, mais sont encore largement utilisées dans les databooks des

fabricants de CMOS.

Lorsque le CMOS a été utilisé pour la première fois

en tant que sous-famille C dans la gamme de circuits intégrés de la série 74,

ses broches d'alimentation ont été renommées VCC et GND, pour se conformer aux

conventions TTL normales, et ce système a ensuite été utilisé sur toutes les

autres sous-familles CMOS utilisé dans la série 74 de circuits intégrés.

Ces derniers temps, ce même système a également commencé à être utilisé sur la série 4000 de circuits intégrés CMOS, et la situation actuelle est qu'une borne d'alimentation positive de circuit intégré CMOS peut être notée VCC ou VDD, selon le caprice du fabricant individuel.