with 2 inputs

with 3 inputs

with 4 inputs

Circuit Intégrée ET (AND)

Les tampon numérique, les portes logiques et les IC logiques

La sortie d'une porte ET passe au niveau haut (vers le niveau logique 1) lorsque toutes ses entrées (A, B et C, etc.) sont au niveau haut.

La manière la plus simple de créer une porte ET consiste à utiliser un certain nombre de diodes et une seule résistance, comme le montre (par exemple) la porte ET dans les figures ci-dessous.

| Porte ET / And Gate | ||

|

à 2 entrées with 2 inputs |

à 3 entrées with 3 inputs |

à 4 entrées with 4 inputs |

|

|

|

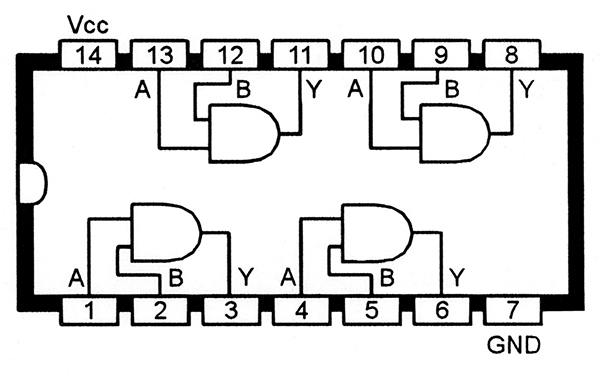

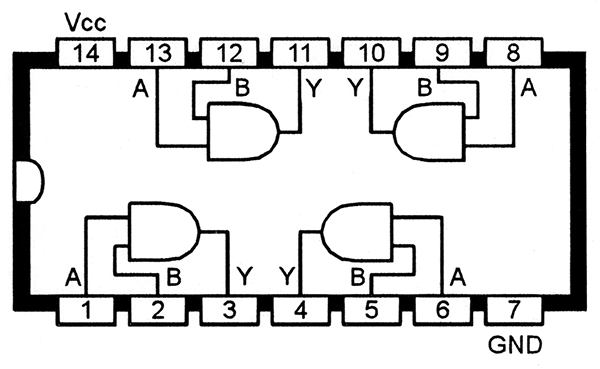

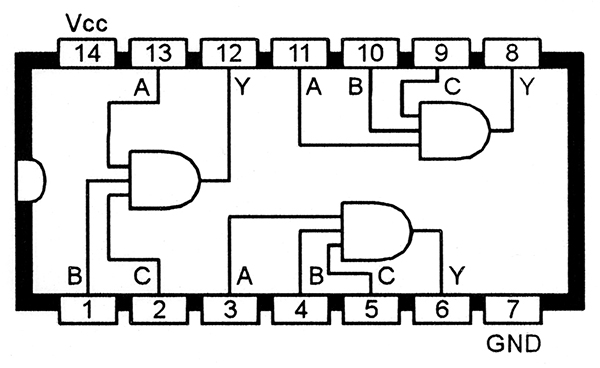

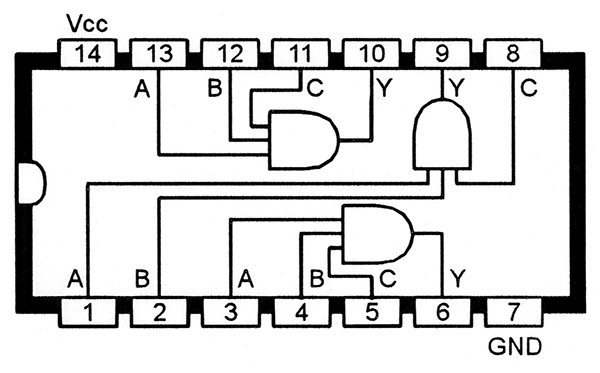

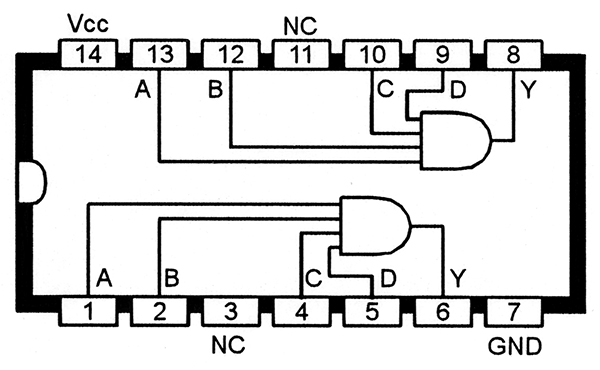

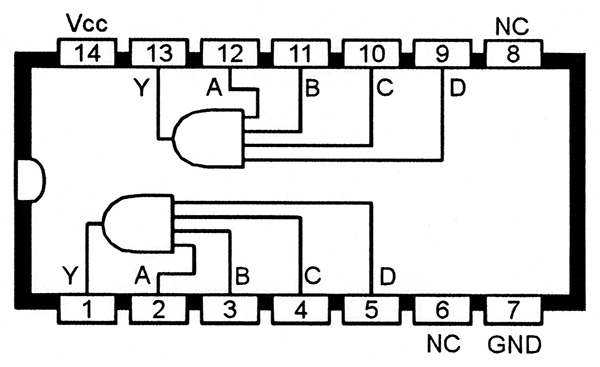

Le tableau ci-dessous répertorie les détails de base de plusieurs circuits intégrés à porte ET populaires ; parmi ceux-ci, les 74LS08, 74HC08 et 4081B (voir les figures ci-dessous) sont des types à quatre entrées ; les 74LS11 et 4073B sont des types à trois entrées, et les 74LS21 et 4082B sont des types à quatre entrées.

| IC | Type | Description |

| 74LS08 | TTL | Quad 2-Input AND Gate |

| 74HC08 | CMOS | Quad 2-Input AND Gate |

| 4081B | CMOS | Quad 2-Input AND Gate |

| 74LS11 | TTL | Triple 3 input AND Gate |

| 4073B | CMOS | Triple 3 input AND Gate |

| 74LS21 | TTL | Dual 4 input AND Gate |

| 4082B | CMOS | Dual 4 input AND Gate |

Figures des Schéma fonctionnel des ICs

| 74LS08 ou 74HC08 | 4081B |

|

|

| 74LS11 | 4073B |

|

|

| 74LS21 | 4082B |

|

|

Lors de l'utilisation de CI à porte ET, chaque porte non-utilisées doit être désactivée en court-circuitant toutes ses entrées ensemble et en les reliant à l'une des lignes d'alimentation du CI.

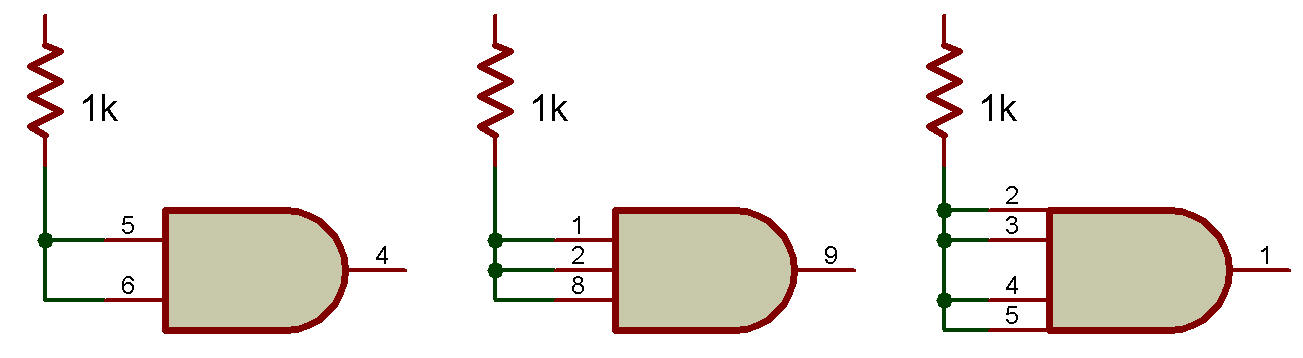

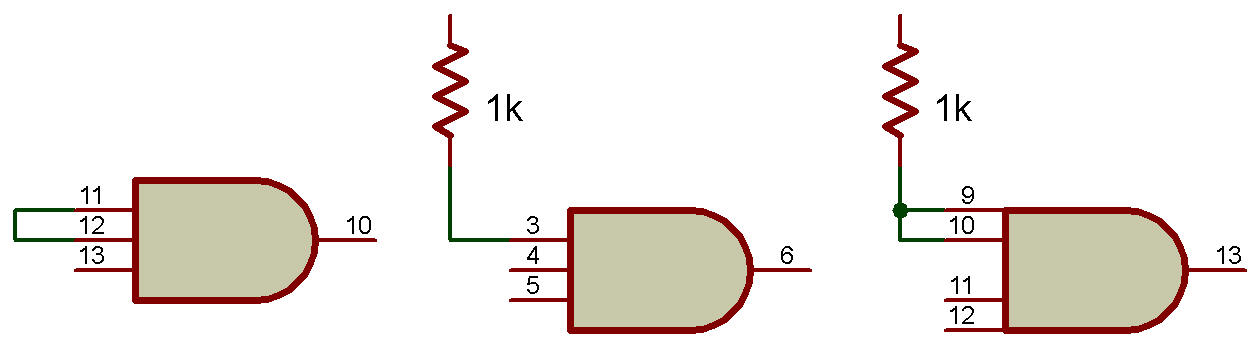

Dans les circuits intégrés CMOS, les entrées en court-circuit peuvent être câblées directement à l'une ou l'autre ligne d'alimentation, mais dans les circuits intégrés TTL, les entrées doivent (pour fournir une consommation de courant de repos minimale avec une bonne stabilité) être liées au rail d'alimentation positif via une seule résistance 1K, comme indiqué dans Figure ci-dessous.

Une seule résistance peut être utilisée comme point de liaison pour un grand nombre de portes non-utilisées.

Méthode de désactivation des portes TTL ET non-utilisées.

Parfois, lorsque vous utilisez trois ou quatre IC de porte ET, vous ne souhaiterez peut-être pas utiliser toutes les bornes d'entrée d'une porte.

Dans ce cas, les entrées indésirables peuvent être désactivées soit en les attachant à un niveau haut (directement dans les portes CMOS, ou via une résistance 1K dans les types TTL), soit en les court-circuitant simplement directement à une entrée utilisée.

La figure ci-dessous montre des exemples de portes TTL ET à trois entrées et quatre entrées câblées pour être utilisées comme deux types d'entrée. Notez que le fan-in d'une porte TTL AND est un 1 presque constant, quel que soit le nombre d'entrées utilisées.

Méthodes de désactivation des entrées TTL indésirables, pour créer une porte ET à deux entrées.

Les portes CMOS ou TTL AND peuvent être converties en tampons non inverseurs en court-circuitant simplement toutes leurs entrées ensemble. La figure 24 montre des exemples de portes TTL AND utilisées comme simples tampons.

![]()

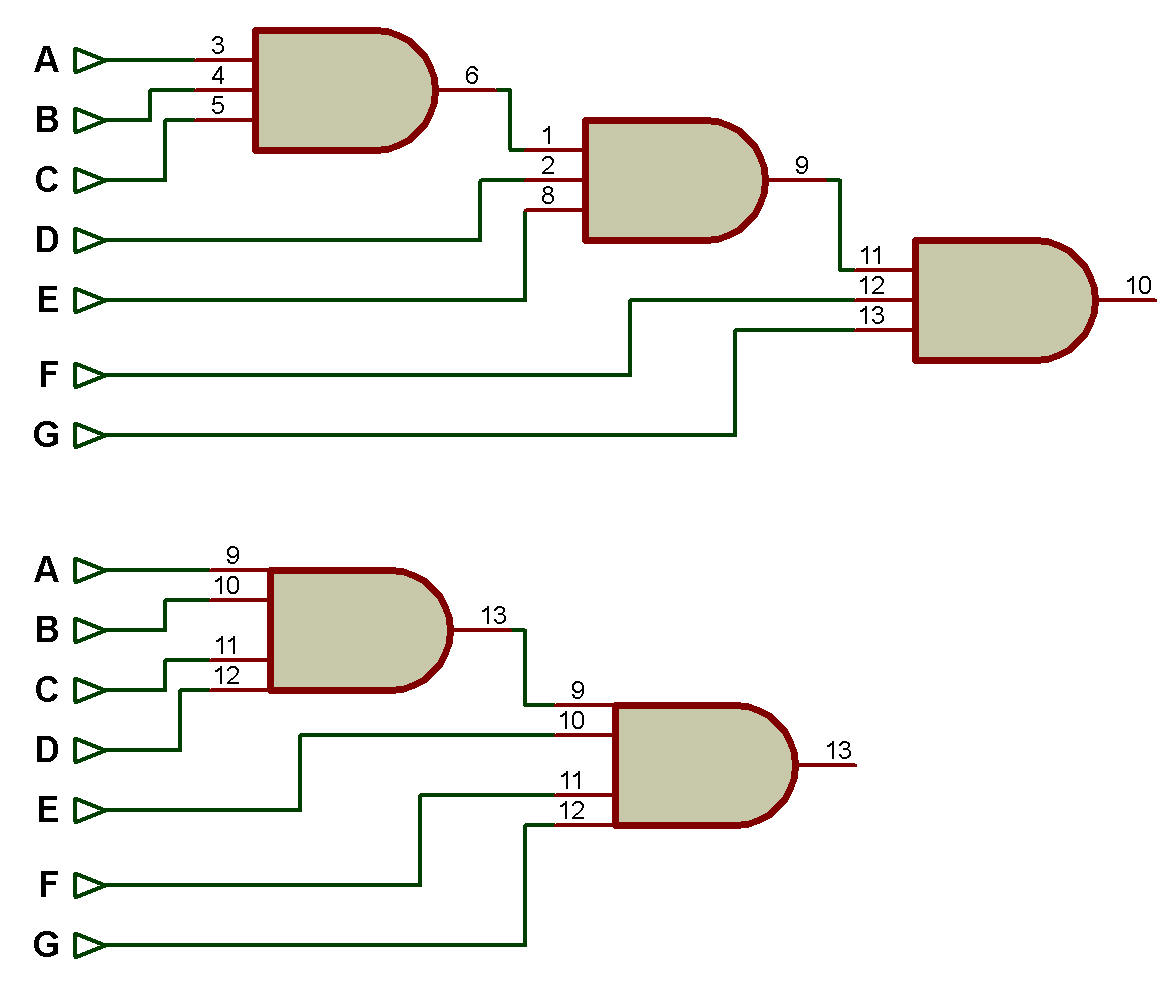

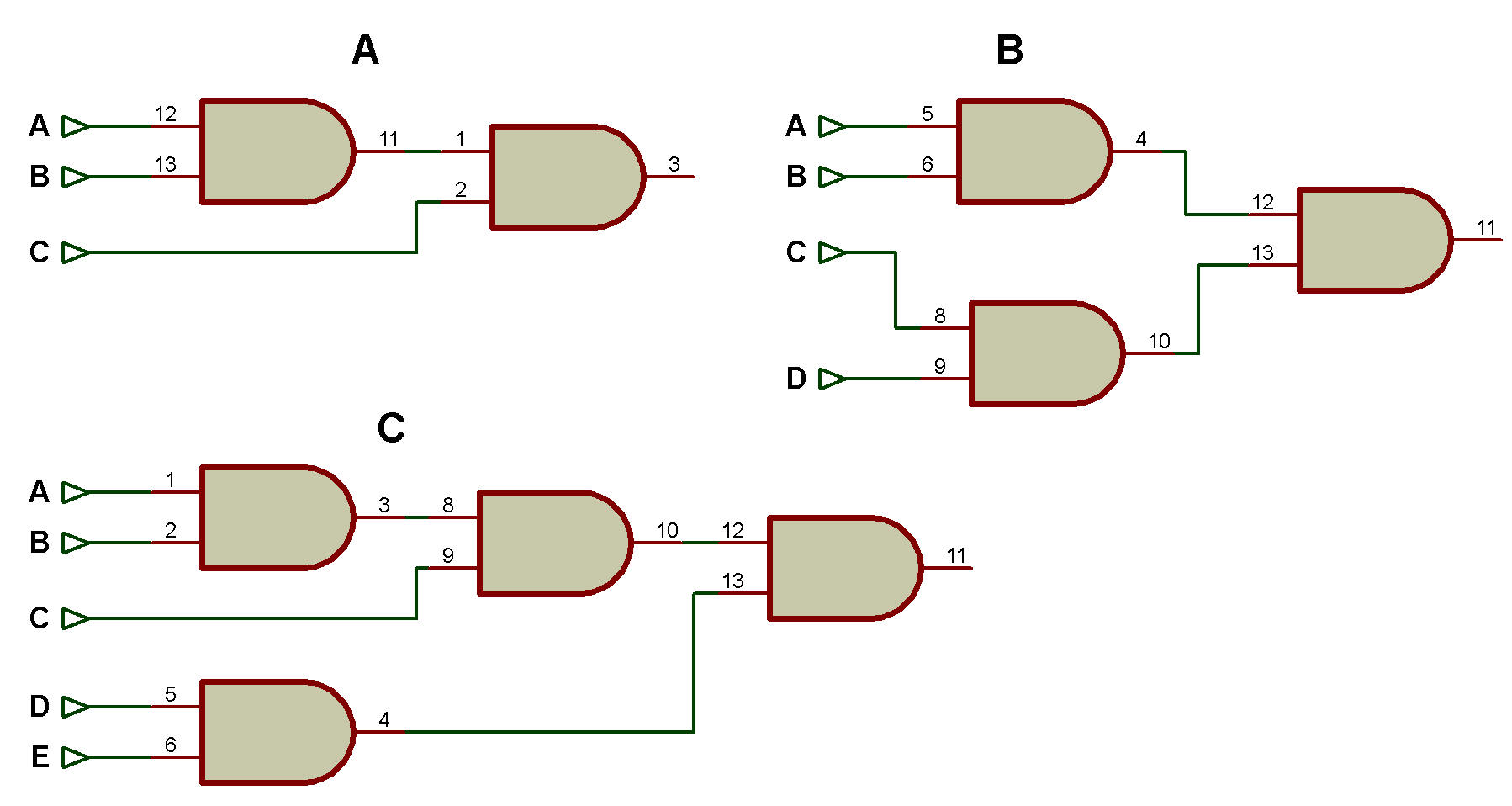

Une caractéristique utile des circuits intégrés de porte ET est que leurs portes peuvent être directement mises en cascade, la sortie d'une porte alimentant directement une entrée d'une autre porte, pour créer des portes ET composées avec n'importe quel nombre d'entrées souhaité.

La figure ci-dessous, par exemple, montre comment deux portes ET d'entrée peuvent être mises en cascade pour créer trois, quatre ou cinq portes ET d'entrée, et la seconde montre trois portes à trois entrées ou deux portes à quatre entrées mises en cascade pour créer une seule porte ET à sept entrées.

Façons d'utiliser deux portes ET à deux entrées pour créer (a) trois entrées, (b) quatre entrées ou (c) portes ET à cinq entrées.

Façons d'utiliser une porte ET à trois entrées ou

une porte ET à quatre entrée pour créer une porte ET à sept entrées.