Les circuits intégrés de la série 74

Les tampon numérique, les portes logiques et les IC logiques

L'électronique numérique moderne est dominée par deux grandes familles de circuits intégrés logiques : la « série 4000 » de circuits intégrés CMOS à faible vitesse et la « série 74 » de circuits intégrés TTL et CMOS rapides.

La famille 74 était à l'origine entièrement basée sur la technologie TTL, qui a fait son apparition sur la scène électronique vers 1972, lorsque la série 74 est soudainement arrivée sous la forme d'une gamme complète de circuits intégrés logiques numériques TTL polyvalents et intelligemment qui étaient chacun conçus pour fonctionner à partir d'une alimentation 5-volts asymétrique et pour s'interconnecter directement et facilement les uns avec les autres sans tracas (chaque sortie peut piloter directement plusieurs entrées).

Cela a rendu relativement facile pour tout ingénieur moyennement compétent la conception et le développement de systèmes logiques numériques assez complexes. La série a connu un succès international instantané et brillant et est devenue presque immédiatement le système logique IC leader au monde.

Ses circuits intégrés

étaient produits à la fois dans des qualités commerciales et militaires et

portaient respectivement les préfixes 74 et 54 ; la gamme de produits

commerciaux est rapidement devenue connue simplement sous le nom de série 74 de

circuits intégrés.

Une caractéristique majeure

de la série 74 est que tous les appareils de la gamme fonctionnent comme des

boîtes noires fonctionnant à des niveaux de seuil d'entrée et de sortie

similaires ; l'utilisateur n'a pas besoin de comprendre leurs circuits internes

pour les utiliser, mais a simplement besoin de connaître leurs règles

d'utilisation de base.

De plus, la sensibilité d'entrée ou « fan-in » de chaque périphérique est conforme à une norme fixe, et sa capacité de commande de sortie ou « fan-out » a une valeur minimale garantie qui indique le nombre d'entrées externes de la série 74 qu'il peut en toute sécurité, conduire directement, ce qui rend très facile l'interconnexion de divers appareils.

La sortie d'une porte 74

avec une sortance de 10 peut piloter directement jusqu'à 10 entrées standard

connectées en parallèle sur d'autres circuits intégrés de la série 74.

Le type de technologie TTL

utilisé dans les premiers circuits intégrés de la série 74 (1972) a donné

naissance à une gamme de dispositifs moyennement rapides mais consommant des

courants assez importants.

En un an environ, des

sous-familles du TTL original ont été introduites, offrant un compromis entre

vitesse et puissance, c'est-à-dire deux fois la vitesse mais à la moitié la

consommation de courant (dans la sous-famille H ou haute vitesse), ou un dixième

de la consommation actuelle mais seulement un tiers de la vitesse normale (dans

la sous-famille L ou basse consommation), etc.

Cette tendance à rechercher

un bon ou un meilleur compromis entre vitesse et consommation d'énergie s'est

poursuivie jusqu'à nos jours, et jusqu'à présent, un total de huit sous-familles

commercialement réussies de TTL (et cinq sous-familles de CMOS) sont apparues.

dans la série 74 de circuits intégrés numériques.

Beaucoup de ces

sous-familles sont par la suite devenues obsolètes, mais l'ingénieur ou le

technicien pratique de conception/maintenance a encore besoin d'une connaissance

de base de chacune d'entre elles, car elles se trouvent souvent dans de vieux

équipements nécessitant une réparation ou une mise à niveau.

Notez que chaque

sous-famille de la série 74 de circuits intégrés est presque directement

compatible avec toutes les autres sous-familles de la série.

Ainsi, si vous ouvrez un ancien équipement et découvrez (par exemple) qu'un ancien CI de compteur de décades 74L90 doit être remplacé mais n'est plus disponible, vous découvrirez probablement qu'un CI de compteur de décades 74LS90 moderne peut être utilisé comme prise directe en remplacement, ou que tout autre CI 74XX90 peut être utilisé en remplacement soit directement, soit avec une légère modification du circuit (en fonction des caractéristiques de base des deux sous-familles).

Dans les deux cas, la première chose à faire est d’identifier l’appareil qui vous intéresse à partir de son numéro de code imprimé.

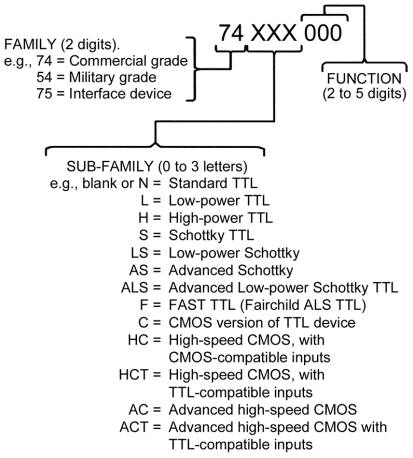

La figure 1 explique le schéma de base utilisé pour formater les numéros de code de la série 74.

FIGURE 1. Système de codage de base utilisé sur les circuits intégrés de la série 74.

Tous les CI de la famille 74 sont identifiés par un code alphanumérique qui, dans sa forme la plus simple, se compose de trois sous-codes liés ensemble, comme le montre la figure 1.

Le premier sous-code (à gauche) se compose de deux chiffres qui lire 74, 54 ou 75.

Le 74 identifie le circuit intégré comme un membre de qualité commerciale de la famille. Ces appareils sont généralement encapsulés dans un boîtier double en ligne (DIP) en plastique à 14, 16 ou 24 broches, peut être utilisé avec des alimentations comprises dans la limite de +4,75 V à +5,25 V et peut fonctionner sur la plage de température 0 °C à +70°C.

Le 54 identifie l'IC comme un membre de la famille de qualité militaire de haute qualité.

Ces dispositifs sont encapsulés dans des boîtiers exotiques, peuvent utiliser des alimentations dans la limite de +4,5 V à +5,5 V et peuvent fonctionner dans la plage de températures de -55 °C à +125 °C.

Le 75 identifie le CI

comme un circuit intégré de qualité commerciale, périphérique d'interface conçu

pour prendre en charge la gamme d'appareils 74.

Le deuxième sous-code

(central) comprend jusqu'à trois lettres et identifie la technologie ou la

sous-famille précise utilisée dans la construction de l'appareil, comme indiqué

dans le schéma.

Notez que les appareils TTL standard ne portent aucun code central ou un N.

Chacun des sept autres

appareils principaux de la sous-famille TTL porte un code d'identification

central, et les cinq principales sous-familles CMOS 74 portent un code central

qui inclut le lettre C.

Le dernier sous-code (à

droite) se compose généralement de deux à cinq chiffres (mais inclut parfois une

lettre A ou une étoile) et identifie la fonction précise du circuit intégré (par

exemple, porte NAND quadruple à deux entrées, compteur de décades, registre à

décalage de quatre bits, etc.).

La relation précise entre

ce sous-code et la fonction de l’appareil peut être déterminée à partir des

listes du fabricant.

Ainsi, un circuit intégré de

type 74 peut porter un code qui, dans sa forme la plus simple, lit quelque chose

comme 7400, 74N00 ou 7414, etc., s'il s'agit d'un périphérique TTL standard, ou

74L14, 74LS38 ou 74HC03, etc. s'il s'agit d'un autre sous-membre de la famille

74.

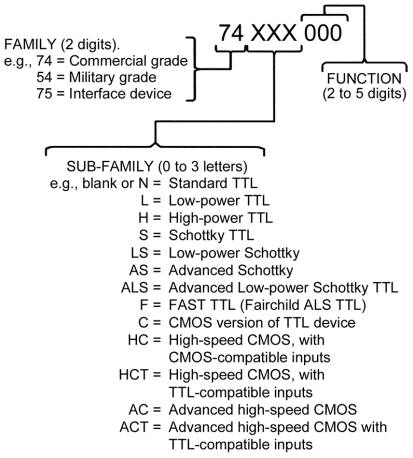

Notez qu'en pratique, les CI de la série 74 portent souvent une forme élaborée du code de base qui comprend un préfix de deux lettres identifiant le fabricant, plus un suffixe du fabricant qui indique le style d'emballage, etc., comme indiqué dans Figure 2.

FIGURE 2. Le code de base de la série 74 est souvent élaboré avec le préfixe et/ou le suffixe du fabricant.

Par conséquent, un dispositif marqué SN74LS90N est un circuit intégré 74LS90 normal, fabriqué par Texas Instruments et logé dans un DIP en plastique.

SOUS-FAMILLES TTL

Huit sous-familles

majeures de TTL ont été utilisées dans la série 74 tout au long de sa durée de

vie, comme suit :

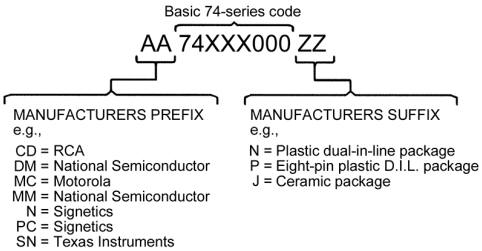

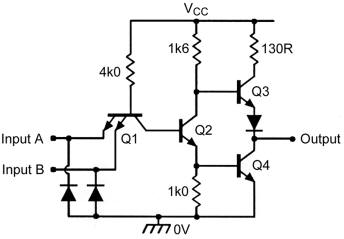

TTL standard

Le TTL standard est similaire au type de base déjà décrit, sauf que chacune de ses entrées est équipée d'une diode de protection qui aide à supprimer les transitoires et accélère son action de commutation.

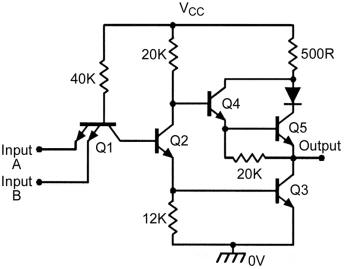

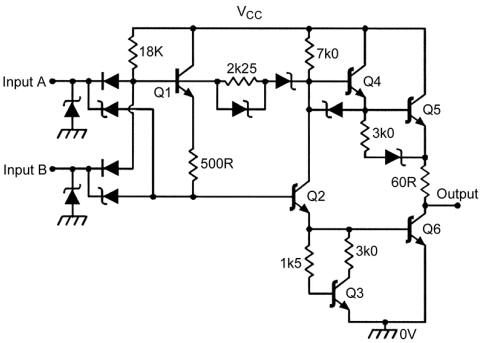

La figure 3 montre le circuit réel d'une porte NAND 7400 à deux entrées. Sa consommation électrique est de 10 mW et son délai de propagation est de 9 nS lors du pilotage d'une charge de 15pF/400Ω.

FIGURE 3. Circuit d'une porte NAND à deux entrées standard TTL 7400.

TTL basse consommation (L) (maintenant obsolète)

Le TTL basse consommation est une version modifiée du type standard, avec ses valeurs de résistance considérablement augmentées pour offrir une réduction spectaculaire de la consommation d'énergie au détriment d'une vitesse réduite.

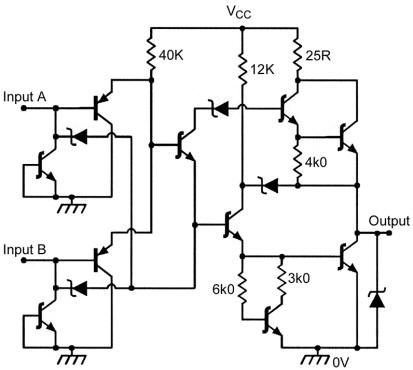

La figure 4 montre le circuit d'une porte NAND à deux entrées 74L00. Sa consommation électrique est de 1 mW et son délai de propagation est généralement de 33 nS.

FIGURE 4. Circuit d'une porte NAND à deux entrées TTL 74L00 basse consommation (L).

TTL haute vitesse (H) (maintenant obsolète)

Le TTL haute vitesse est une version modifiée du type standard, avec ses valeurs de résistance réduites pour donner une augmentation de la vitesse au détriment d'une consommation d'énergie accrue.

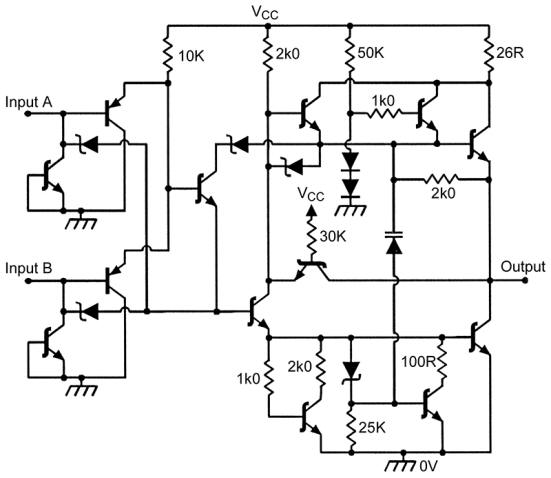

La figure 5 montre le

circuit d'une porte NAND à deux entrées 74H00. Sa consommation électrique est de

22 mW et son délai de propagation est typiquement de 6 nS.

FIGURE 5. Circuit d'une

porte NAND à deux entrées TTL 74H00 à grande vitesse (H).

Schottky (S) TTL (maintenant obsolète)

Un commutateur à transistor peut être conçu pour donner une action de commutation saturée ou insaturée.

La commutation saturée – dans

laquelle la tension du collecteur du transistor tombe bien en dessous de celle

de la base dans des conditions passantes – est très facile à mettre en œuvre,

mais produit des délais de propagation environ 2,5 fois plus longs que ceux

disponibles dans les circuits non saturés.

Le TTL standard fait

fonctionner ses transistors dans un mode de commutation fortement saturé dans

lequel le collecteur tombe à environ 400 mV en dessous de la base en condition

passante, et est donc intrinsèquement lent.

Schottky TTL, quant à lui, fait

fonctionner ses transistors dans un mode de commutation légèrement saturé dans

lequel le collecteur ne tombe qu'à environ 180 mV en dessous de la tension de

base dans des conditions passantes, et est presque aussi rapide qu'un circuit

non saturé (tel qu'un ECL).

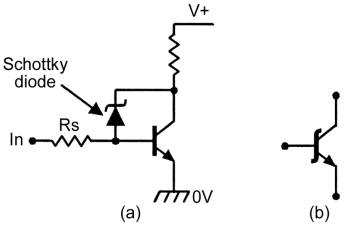

Fondamentalement, cette action est obtenue

en connectant une diode Schottky (qui agit rapidement et présente une chute de

tension directe typique de seulement 180 mV) entre le collecteur et la base du

transistor, comme le montre la figure 6 (a), dans laquelle Rs représente

l'entrée de l'impédance de la source de l'impulsion.

FIGURE 6. (a) Une diode Schottky utilisée pour limiter la profondeur de saturation d'un transistor NPN ; (b) Symbole d'un transistor NPN « Schottky », avec une diode de serrage intégrée entre son collecteur et sa base.

Ainsi, si le collecteur devient négatif de plus de 180 mV par rapport à la base, la diode Schottky devient polarisée en direct et commence à dériver le courant de base directement dans le collecteur du transistor, empêchant ainsi automatiquement une saturation plus profonde.

En réalité, la diode Schottky peut facilement être incorporée dans la structure du transistor, et un « transistor à serrage Schottky » de ce type utilise le symbole indiqué en (b).

Dans un circuit intégré Schottky TTL pratique, les transistors à serrage Schottky sont largement utilisés et la plupart des valeurs de résistance sont réduites, ce qui donne une bonne augmentation de la vitesse au détriment de la consommation d'énergie.

L'étage de sortie totem-pôle utilise une paire de transistors Darlington pour donner un pull-up actif, ainsi qu'un réseau pull-down actif modifié qui donne une action de quadrature de forme d'onde améliorée.

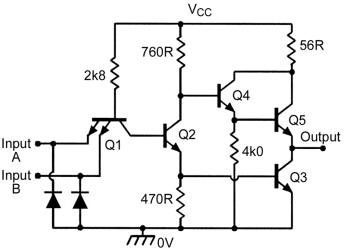

La figure 7 montre le circuit d'une porte NAND à deux entrées 74S00. Sa consommation électrique est de 20 mW et son délai de propagation est de 3 nS lors du pilotage d'une charge de 15pF/280Ω.

FIGURE 7. Circuit d'une porte NAND à deux entrées Schottky (S) TTL 74S00.

Low-Power Schottky (LS) TTL

Schottky basse consommation utilise une forme modifiée de la technologie Schottky, utilisant des techniques de fabrication améliorées, combinée à une forme de réseau d'entrée à diode-transistor (plutôt que multi-émetteurs) qui a une impédance élevée et donne une commutation rapide.

La figure 8 montre le circuit

d'une porte NAND à deux entrées 74LS00. Sa consommation électrique est de 2 mW

et son délai de propagation est de 8 nS lors du pilotage d'une charge de

12pF/2K.

FIGURE 8. Circuit d'une porte NAND à deux entrées Schottky (LS)

TTL 74LS00 basse consommation.

Advanced Low-Power Schottky (ALS) TTL

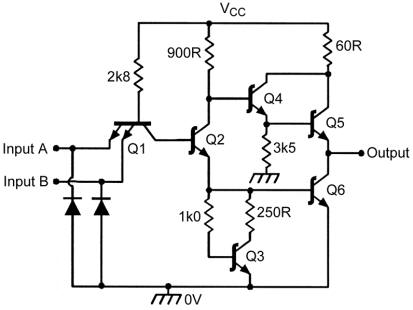

Cette sous-famille est similaire au LS mais utilise un processus de fabrication avancé qui, combiné à des modifications de conception mineures, produit des dispositifs actifs plus rapides et offrant des gains plus élevés que les types LS.

La figure 9 montre le circuit d'une porte NAND à deux entrées 74ALS00. Sa consommation électrique est de 1 mW et son délai de propagation est de 4 nS lors du pilotage d'une charge de 50pF/2K.

FIGURE 9. Circuit d'une porte NAND avancée à deux entrées Schottky (ALS) 74ALS00 à faible consommation.

Advanced Schottky (AS) TTL

Cette sous-famille est similaire à l'ALS, mais sa conception est optimisée pour offrir une vitesse très élevée au détriment de la consommation d'énergie.

La figure 10 montre le circuit

d'une porte NAND à deux entrées 74AS00. Sa consommation électrique est de 22 mW

et son délai de propagation n'est que de 2 nS lors du pilotage d'une charge de

50pF/2K.

FIGURE 10. Circuit d'une porte NAND avancée à deux entrées

Schottky (AS) TTL 74AS00.

FAST (F) TTL

FAST (Fairchild Advanced Schottky TTL) est la version Fairchild de « AS » TTL.

Il est fabriqué sous licence par plusieurs sociétés (dont Philips et National Semiconductor). Ses performances sont similaires (en termes de vitesse et de consommation électrique) à celles de la sous-famille AS.

SOUS-FAMILLES SÉRIE 74 CMOS

Lorsque la série 74 de circuits intégrés a été lancée pour la première fois en 1972, tous les dispositifs de la gamme étaient basés sur la technologie TTL bipolaire, qui consomme par nature une assez grande quantité d'énergie, quelle que soit sa vitesse de fonctionnement.

Vers 1975, la technologie rivale des circuits intégrés numériques CMOS est arrivée sur la scène et, bien qu'elle ne soit pas aussi rapide que le TTL, elle offrait l'avantage exceptionnel d'avoir une consommation d'énergie directement proportionnelle à la vitesse de fonctionnement, étant pratiquement nulle dans des conditions de repos et atteignant la même valeur que TTL à environ 10 MHz.

À la fin des années 1970, le CMOS a été introduit en tant que sous-famille au sein de la gamme de dispositifs de la série 74, portant le code central C.

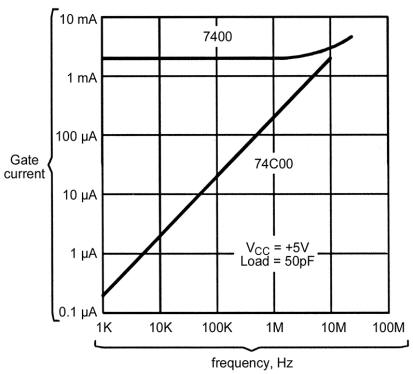

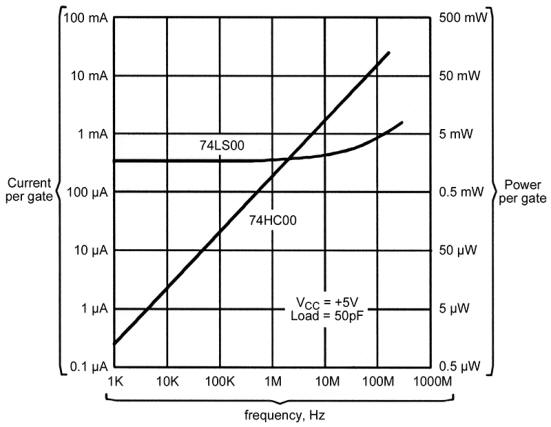

Le graphique de la figure 11 compare les courbes fréquence/consommation de courant d'une seule porte du TTL standard et les versions CMOS C du circuit intégré de porte NAND à deux entrées quad 7400.

FIGURE 11. Graphiques

fréquence-courant de NAND à deux entrées 7400 (TTL) et 74C00 (CMOS)

portes

(avec une entrée carrée).

Dans sa première forme, la sous-famille C de la série 74 était lente et avait une très faible capacité de sortie (son entraînement de sortance était égal à deux entrées de type L).

Cependant, au cours des années suivantes, des améliorations considérables ont eu lieu dans la conception et la production de dispositifs de type CMOS.

Les détails saillants de ce

sujet seront abordés plus en détail dans la partie

LES BASES DU CMOS, mais en attendant, il

suffit de savoir qu'un total de cinq sous-familles CMOS ont été introduites dans

la série 74, comme suit :

CMOS standard (C) (maintenant obsolète)

Cette sous-famille était

constituée de CMOS pratiquement normaux au format série 74. En règle générale,

une seule porte NAND à deux entrées 74C00 consommait environ 15 mW à 10 MHz et

présentait un retard de propagation de 60 nS.

CMOS haute vitesse (HC)

Au début des années 1980, les progrès des techniques de fabrication CMOS ont donné des performances de vitesse similaires à celles du LS TTL, mais avec des niveaux de consommation d'énergie CMOS. Les appareils de la série HC 74 utilisant cette technologie disposent d'entrées compatibles CMOS.

En règle générale, une seule

porte NAND à deux entrées 74HC00 consomme moins de 1 µA de courant de repos et

présente un délai de propagation de 8 nS.

CMOS haute vitesse (HCT)

Il s'agit d'appareils de type HC, mais dotés d'entrées compatibles TTL.

Généralement, une porte NAND à

deux entrées 74HCT00 consomme moins de 1 µA de courant de repos et présente un

délai de propagation de 18 nS.

CMOS avancé haute vitesse (AC)

À la fin des années 1980, les progrès dans la conception CMOS et les techniques de fabrication CMOS ont donné des performances de vitesse similaires à celles de l'ALS. Les appareils de la série AC 74 utilisant cette technologie disposent d'entrées compatibles CMOS.

Généralement, une porte NAND à

deux entrées 74AC00 a un délai de propagation de 5 nS.

CMOS Advanced

High-Speed (ACT)

Il s'agit d'appareils de type AC, mais dotés d'entrées compatibles TTL. Généralement, une porte NAND à deux entrées 74ACT00 a un délai de propagation de 7 nS.

QUELLE FAMILLE LOGIQUE EST LA MEILLEURE ?

Deux grandes familles de logiques à usage général sont actuellement disponibles : la famille CMOS basse vitesse série 4000 et la famille TTL/CMOS haute vitesse série 74 (une troisième famille, utilisant la technologie ECL, est très spécialisée et destinée à être utilisée dans des environnements d'applications à très grande vitesse).

La série 4000 (qui sera décrite dans la partie LES BASES DU CMOS) est particulièrement intéressante dans les circuits fonctionnant en dessous de fréquences de quelques MHz dans lesquels une valeur minimale de consommation de courant de repos est souhaitée.

D'autres avantages majeurs de

la série sont que ses circuits intégrés peuvent fonctionner à partir de

n'importe quelle alimentation dans la plage de 3 à 15 V, avoir une excellente

immunité au bruit et avoir des impédances d'entrée ultra élevées.

La

série 74 présente une valeur particulière dans les circuits fonctionnant à des

fréquences allant jusqu'à plusieurs dizaines de MHz, dans lesquels une faible

consommation de courant de repos n'est pas trop importante et dans lesquels les

circuits intégrés peuvent être alimentés à partir d'une alimentation CC bien

régulée (généralement de +5 V).

Si vous décidez d'utiliser un CI de la série 74, vous êtes confronté au problème de savoir « quelle sous-famille convient le mieux à mon application ? »

QUELLE SOUS-FAMILLE DE LA SÉRIE 74 EST LA MEILLEURE ?

Lors de la conception d'un nouveau circuit logique, les circuits intégrés doivent toujours être sélectionnés sur la base d'une supériorité commerciale (plutôt que purement technique).

Il serait, par exemple, insensé d'utiliser une porte ALS très rapide dans une application dans laquelle un dispositif LS ou HC plus lent serait parfaitement adéquat et serait facilement disponible à une fraction du coût du dispositif ALS.

En gardant ce point à l’esprit, notez que les cinq sous-familles de circuits intégrés de la série 74 les plus largement disponibles au moment de la rédaction sont Standard et LS TTL, ainsi que HC, HCT et AC CMOS.

Parmi ceux-ci, le standard TTL est techniquement et commercialement inférieur au LS et son utilisation n'est pas recommandée dans les nouvelles conceptions.

Le CMOS AC coûte environ 2,5 fois plus cher que le LS TTL ou le HC/HCT CMOS et ne doit donc être utilisé que dans des applications spéciales.

HCT est uniquement destiné à

être utilisé en remplacement des dispositifs TTL dans les conceptions existantes

et ne doit pas vraiment être utilisé dans les nouvelles conceptions. Il ne reste

que LS TTL et HC CMOS.

Parmi ces deux sous-familles de la série 74, LS

est légèrement plus rapide que HC et est disponible dans une gamme bien plus

large de types de dispositifs fonctionnels, mais consomme généralement plus de

courant/puissance d'alimentation que HC à des fréquences inférieures à environ 5

MHz.

La Figure 12 compare les

performances des portes 74LS00 et 74HC00.

FIGURE 12. Graphiques

fréquence/courant/puissance des portes NAND à deux entrées 74LS00 et 74HC00

(avec une entrée d'onde carrée).

Ainsi, pour la plupart des nouvelles applications de conception, les

sous-familles LS TTL et HC CMOS méritent une récompense conjointe « meilleure »,

avec peut-être un léger avantage pour LS.

NIVEAUX LOGIQUES TTL ET IMMUNITÉ AU BRUIT

Tous les circuits intégrés numériques gèrent les signaux d'entrée et de sortie qui basculent entre les états haut (logique 1) ou bas (logique 0).

En TTL, chacun de ces niveaux logiques doit se situer dans une plage définie de limites de tension.

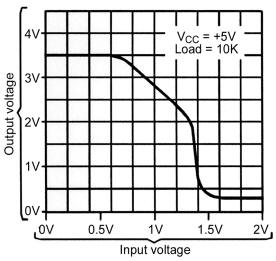

La figure 13 montre la

courbe de tension entrée-sortie typique d'un onduleur TTL standard qui

fonctionne à partir d'une alimentation +5 V et a une sortie légèrement chargée.

FIGURE 13. Graphique de tension entrée-sortie Standard-TTL

Notez que la sortie est élevée,

à +3,5 V, jusqu'à ce que l'entrée monte à 0,7 V, puis diminue de manière assez

linéaire à mesure que l'entrée augmente encore, et finit par se stabiliser à une

valeur faible d'environ 0,25 V lorsque l'entrée dépasse 1,5 V. .

En

pratique, tous les circuits intégrés Standard et LS TTL sont garantis,

lorsqu'ils utilisent une alimentation +5 V, de reconnaître toute tension

d'entrée allant jusqu'à 0,8 V comme étant une entrée logique 0 et de 2,0 V ou

plus comme étant une entrée logique 1.

Notez que la zone située entre

ces deux niveaux est connue sous le nom de zone ou région indéterminée du CI, et

toute opération dans cette zone doit être évitée.

Dans les circuits TTL,

différents niveaux logiques sont utilisés pour définir les signaux d'entrée et

de sortie, car les niveaux de tension de sortie TTL varient considérablement en

fonction des conditions de charge.

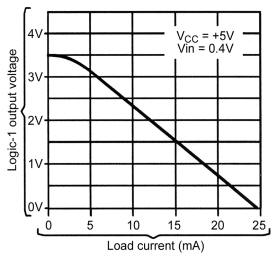

La figure 14 montre comment —

lorsqu'une entrée de 0,4 V est appliquée à l'onduleur TTL ci-dessus — la tension

de sortie logique 1 passe de +3,5 V à un courant de charge proche de zéro, à

seulement 2,0 V à un courant de charge de 13 mA, et ainsi de suite.

FIGURE 14. Graphique tension-courant de sortie logique TTL standard-1

En pratique, tous les circuits intégrés TTL standard sont garantis (lors de l'utilisation d'une alimentation +5 V) pour reconnaître toute tension de sortie allant jusqu'à 0,4 V comme étant une sortie logique 0, et de 2,4 V ou plus comme étant une sortie logique 1.

Sur les circuits intégrés LS

TTL, ces niveaux sont de 0,5 V pour le 0 logique et de 2,7 V pour le 1 logique.

Lorsqu'une sortie TTL est connectée directement à une entrée TTL suivante,

tout bruit excessif sur le signal de sortie peut entraîner un fonctionnement

incorrect de l'étage d'entrée suivant.

Ainsi, dans le pire des cas,

une sortie TTL standard logique 1 peut être aussi faible que 2,4 V, et toute

impulsion de bruit négative superposée supérieure à 0,4 V entraînera l'entrée

suivante en dessous du « 0 logique » de 2,0 V, seuil défini et peut l'amener à

reconnaître par erreur son entrée comme étant un signal logique 0 (plutôt que

logique 1).

L'ampleur maximale du bruit dans le pire des cas qu'un CI

numérique peut ignorer dans ces conditions est connue sous le nom d'immunité au

bruit ou de valeur de marge de bruit, et est égale à la différence entre les

valeurs de seuil de sortie/entrée logique 0 ou logique 1.

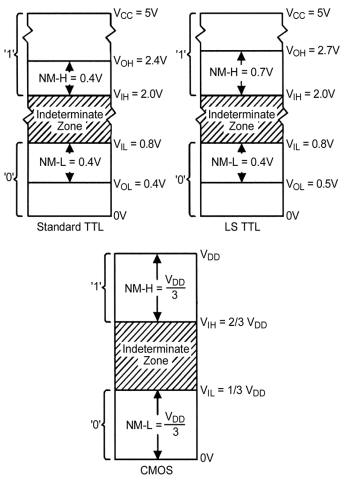

Avec la norme TTL, les marges de bruit pour la logique 1 (NM-H) et la logique 0 (NM-L) ont défini les valeurs les plus défavorables de 400 mV.

Avec LS TTL, les marges de bruit sont de 700 mV pour le logique 1 et de 300 mV pour le logique 0.

Avec CMOS, les deux marges ont des valeurs de VDD/3.

La figure 15 illustre les valeurs de ces trois ensembles de valeurs de seuil et de marge.

FIGURE 15. Valeurs de niveau logique et de marge de bruit de Standard TTL, LS TTL et CMOS

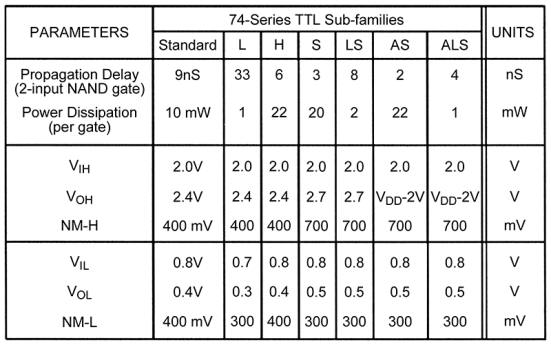

La figure 16 développe les

informations ci-dessus et montre les valeurs réelles de tension de seuil et de

marge de bruit, ainsi que les valeurs typiques de propagation et de dissipation

de puissance pour des portes NAND uniques à deux entrées de type 00, pour les

sept principales sous-familles de TTL (FAST TTL est considérée ici comme une

simple variation mineure de l'AS TTL).

FIGURE 16. Valeurs typiques du

délai de propagation et de la dissipation de puissance pour des portes NAND

uniques de type 00 dans les plages de la sous-famille TTL, ainsi que les valeurs

de seuil de tension et de marge de bruit de la sous-famille.

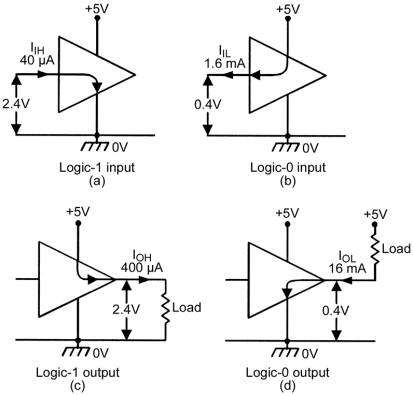

FAN-IN ET FAN-OUT

Dans les circuits TTL, les exigences de commande d'entrée d'un élément sont connues sous le nom de valeurs de sortance, et ses limites de capacité de commande de sortie sont connues sous le nom de valeurs de sortie.

La figure 17 illustre la signification et les valeurs les plus défavorables de ces éléments lorsqu'ils sont appliqués à un élément TTL standard.

FIGURE 17. Paramètres d'entrée et de sortie de base d'un élément logique TTL standard

Ainsi, (a) montre que lorsque l'élément TTL est piloté à partir d'un étage de sortie TTL standard, il consomme un courant d'entrée (IIH) dans le pire des cas de 40 µA lorsqu'il est alimenté par une entrée logique 1 de 2,4 V, mais - comme indiqué dans (b) - alimente 1,6 mA (IIL) dans le pilote lorsqu'il fournit une entrée logique 0 de 0,4 V.

Le diagramme (c) montre que la

sortie de l'élément TTL peut, lorsqu'elle est dans l'état logique 1, fournir

jusqu'à 400 µA (IOH) avant que sa tension de sortie ne tombe en dessous de 2,4

V ; il est ainsi capable d'alimenter jusqu'à 10 entrées Standard, et est dit

avoir une sortance logique 1 (= IOH/IIH) de 10.

De même, (d) montre que

l'étage de sortie peut - lorsqu'il est à l'état logique 0 - absorber jusqu'à 16

mA avant que sa tension de sortie ne tombe en dessous de 0,4 V ; il est ainsi

capable de piloter jusqu'à 10 entrées standard et est dit avoir une sortance

logique 0 (= IOL/IIL) de 10.

Ainsi, l'élément a une sortance

dans le pire des cas de 10, et il peut être utilisé pour piloter directement

jusqu’à 10 entrées standard.

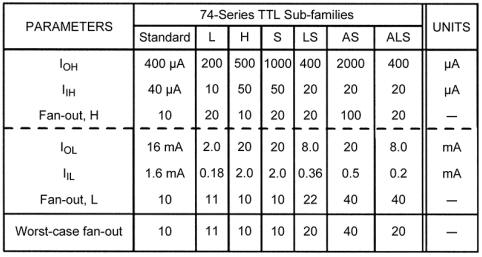

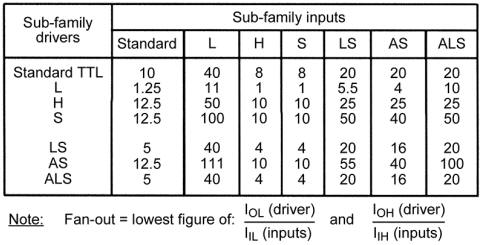

La figure 18 présente les données ci-dessus

sous forme de tableau, ainsi que des données similaires pour toutes les autres

sous-familles TTL majeures.

FIGURE 18. Valeurs de diffusion et de

diffusion des principales sous-familles TTL.

Lorsque vous travaillez au sein d’une sous-famille, notez que le chiffre le plus important ici est la valeur de « sortance dans le pire des cas (F-O) ».

Ainsi, si vous concevez (par exemple) un système entièrement basé sur des circuits intégrés LS, vous pouvez connecter en toute confiance une sortie ordinaire directement à jusqu'à 20 entrées normales, sans risque de dysfonctionnement dû à une surcharge (si vous devez piloter plus de circuits), pour plus de 20 entrées, vous pouvez le faire via un ou plusieurs tampons à grande diffusion, etc.).

Notez que, au sein d'une

sous-famille donnée, toutes les entrées ordinaires sont censées (dans le jargon

TTL) avoir un éventail d'unité (1), mais qu'en pratique certains circuits

intégrés MSI ou LSI (tels que les compteurs et les registres, etc. ) peut avoir

des entrées spéciales (telles que Réinitialisation ou Préréglage, etc.) avec des

valeurs d'entrée de fan-in égales ou supérieures à deux.

Parfois, un

ingénieur peut être amené à mélanger des sous-familles TTL, généralement afin

qu'un circuit intégré obsolète puisse être remplacé par un plug-in moderne et

facilement disponible.

Dans un tel cas, il est nécessaire de relier les données de sortance d'une sous-famille à celles d'une autre, pour vérifier que le mixage peut se faire sans provoquer de surcharge en entrée ou en sortie.

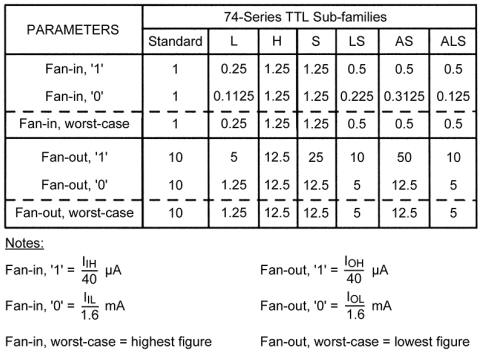

Un moyen simple d'y parvenir consiste simplement à transposer les données de la figure 18 dans des unités de fan-in « TTL standard », comme le montre la figure 19, pour avoir une idée approximative des valeurs relatives des fan des différentes sous-familles.

Ainsi, on peut voir d'un coup

d'œil que le LS TTL n'a que la moitié des exigences de diffusion en entrée du

TTL standard, mais n'a également que la moitié de sa capacité de diffusion, etc.

FIGURE 19. Fan-in et fan-out TTL en termes d'unités TTL standard.

Un moyen encore plus utile

d'appliquer les données de base de la figure 18 consiste à les convertir en un

formulaire facile à utiliser qui relie les données de sortance et de sortie de

chaque sous-famille TTL à toutes les autres sous-familles TTL, comme illustré.

dans la figure 20.

FIGURE 20. Nombre maximum d'entrées TTL pouvant être

pilotées à partir de n'importe quelle sortie de sous-famille TTL.

Ici, en lisant les colonnes de

gauche, on peut (par exemple) voir qu'une sortie LS normale peut piloter jusqu'à

cinq entrées TTL standard, et qu'une sortie TTL standard peut piloter en toute

sécurité jusqu'à 20 entrées LS.

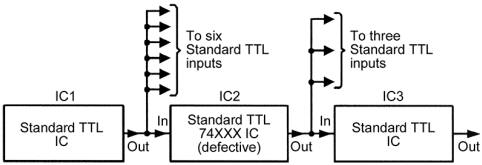

Ainsi, si un ingénieur est confronté à un

problème tel que celui illustré sur la figure 21, dans lequel un défaut sur un

ancien circuit TTL standard est attribué à un circuit intégré de type 74XXX

(IC2) défectueux qui est utilisé pour piloter directement quatre autres circuits

TTL standard.

On peut rapidement voir qu'un

CI équivalent enfichable 74LSXXX peut être utilisé en toute sécurité pour

remplacer directement le dispositif TTL standard IC2 sans encourir de problèmes

de surcharge.

FIGURE 21. IC2 est défectueux ; il s'agit d'un appareil TTL

standard. Peut-il être remplacé directement par un IC 74LSXXX ? La figure 20

montre que la réponse est oui.

RÈGLES D'UTILISATION DE BASE TTL

Il est généralement assez simple de concevoir des circuits logiques utilisant des circuits intégrés TTL, à condition qu'un ensemble de règles d'utilisation de base TTL soient respectées.

En supposant que la question du fan-in et du fan-out ait déjà été réglée, il existe quatre thèmes d'utilisation de base en suspens, et ceux-ci seront décrits dans notre prochain section, sous les titres généraux d'alimentations, signaux d'entrée, entrées inutilisées et Interfaçage.