Familles Logiques

Les tampon numérique, les portes logiques et les IC logiques

Des circuits logiques numériques et des circuits intégrés pratiques peuvent être construits à l'aide de diverses technologies.

La première famille réussie de circuits intégrés logiques numériques est apparue au milieu des années 1960. Ceux-ci utilisaient une alimentation de 3,6 V et employaient une technologie simple connue sous le nom de logique résistance-transistor, ou RTL.

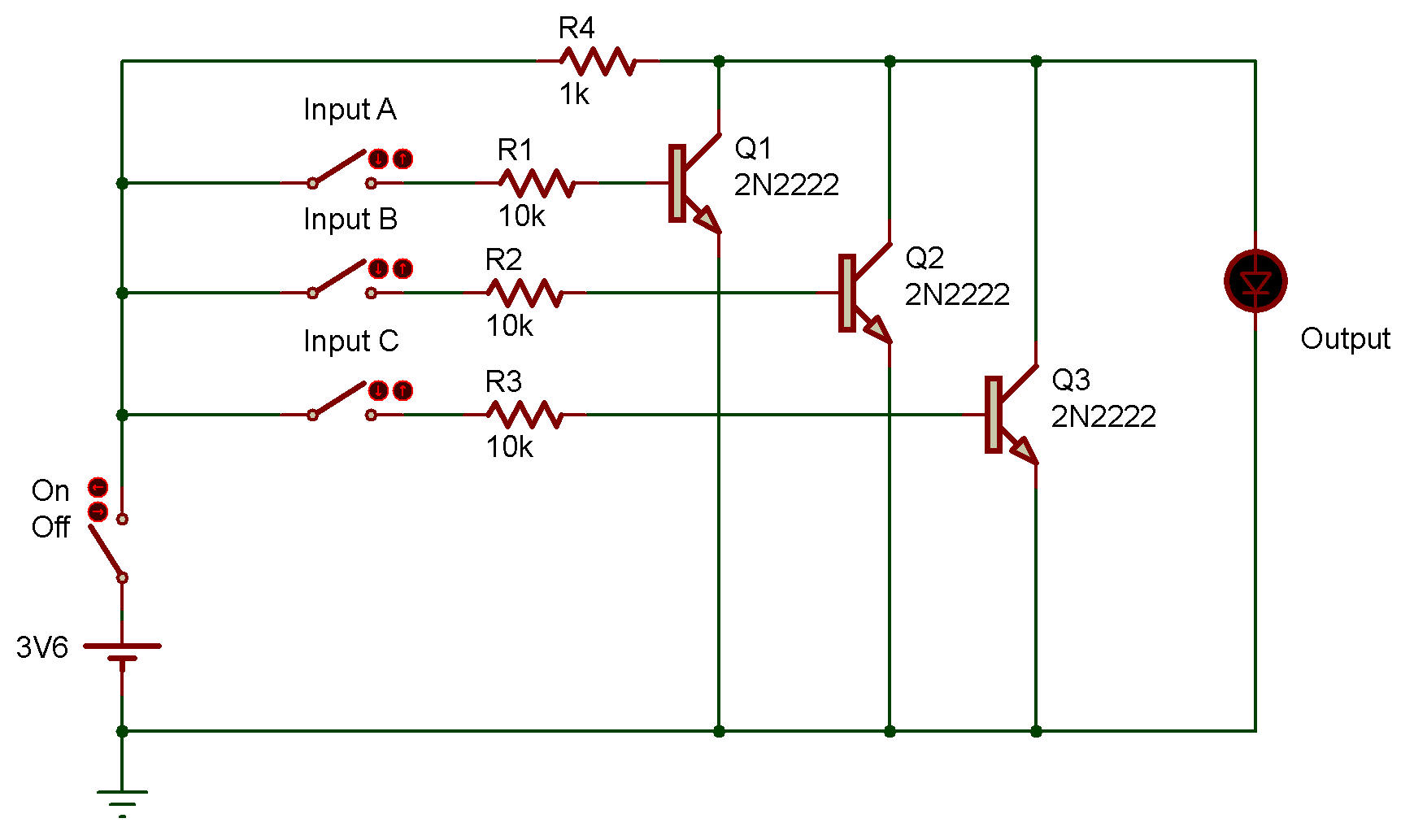

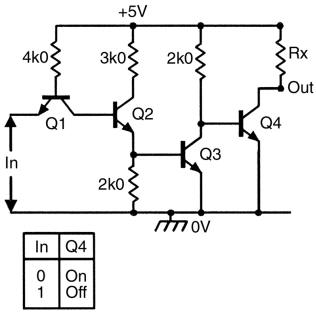

La figure 12 montre le circuit de base d'une porte RTL NOR à trois entrées.

FIGURE 12. Version IC d'une porte RTL NOR à trois entrées.

RTL fonctionnait plutôt lentement, avec un délai de propagation typique (le temps nécessaire à un seul front d'impulsion ou à une transition pour passer de l'entrée à la sortie) de 40 nS dans une porte de faible puissance, ou de 12 nS dans une porte de puissance moyenne. RTL est désormais obsolète.

Un autre type précoce de technologie logique IC, développé à la fin des années 1960, était basé sur des développements simples des types discrets de circuits logiques illustrés dans les figures 4 à 7 (Les IC logiques numériques) et était connu sous le nom de logique à diode-transistor, ou DTL.

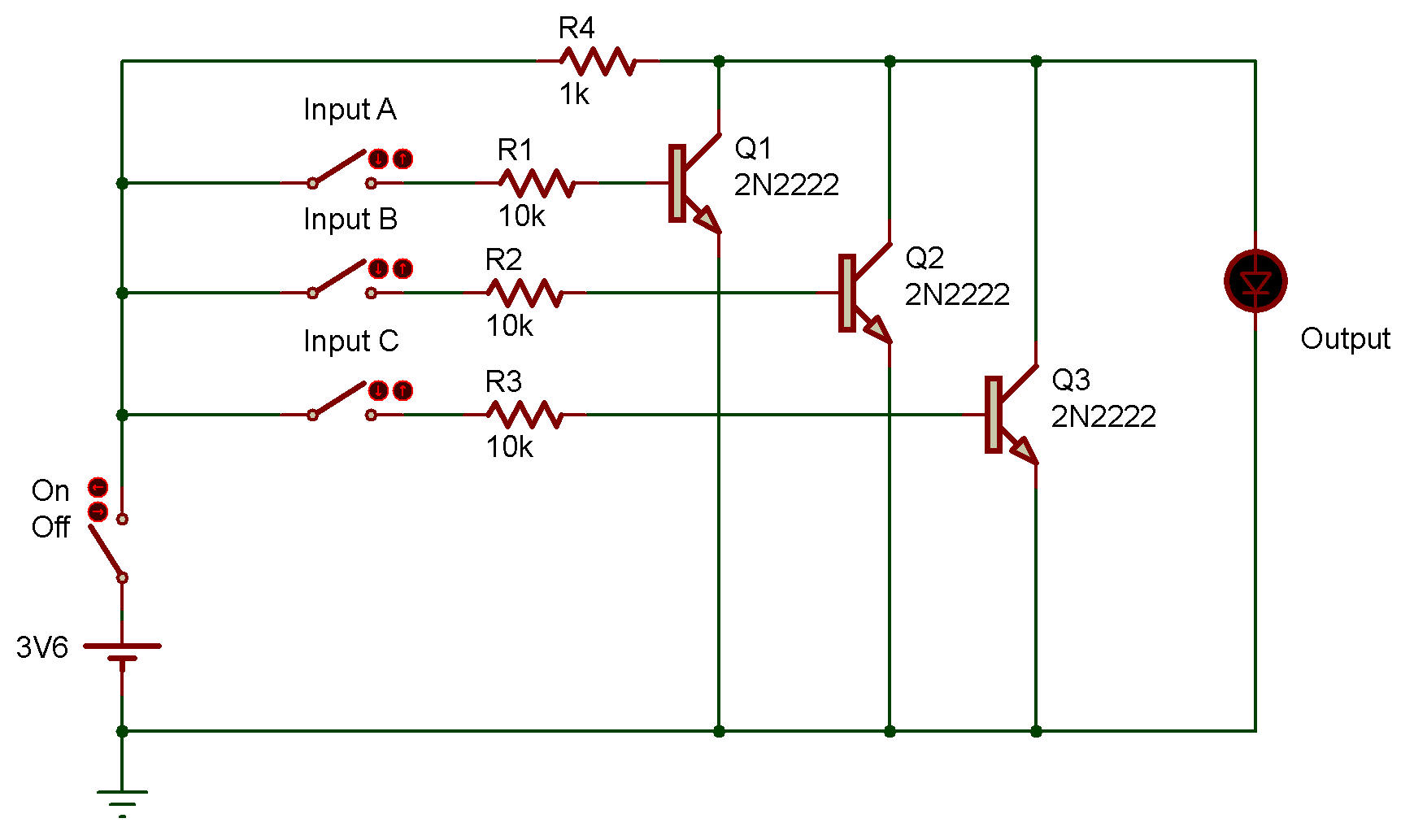

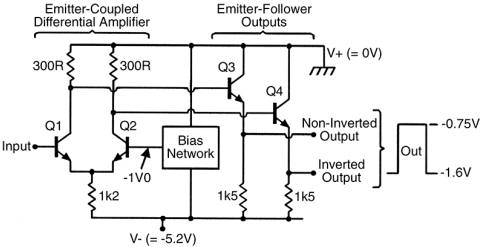

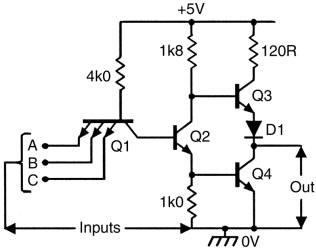

La figure 13 montre le circuit de base d'une porte DTL NAND à trois entrées. DTL utilisait une alimentation double de 5 volts, donnait un retard de propagation typique de 30 nS et donnait une sortie inférieure à 0,4 V dans l'état logique 0 et supérieure à 3,5 V dans l'état logique 1. DTL est désormais obsolète.

FIGURE 13. Version IC d'une porte DTL NAND à trois entrées.

NAND DTL

Entre la fin des années 1960 et le milieu des années 1970, plusieurs autres technologies logiques IC prometteuses sont apparues.

La plupart d’entre eux ont rapidement disparu dans l’oubli. Parmi ceux qui sont apparus, ont disparu ou ont perdu de leur importance, citons HTL (High Threshold Logic), ECL (Emitter Coupled Logic) et PML (P-type MOSFET Logic).

La plus durable de ces

technologies était l'ECL, qui est toujours en production et permet un

fonctionnement très rapide, mais au prix d'une consommation de courant/énergie

très élevée.

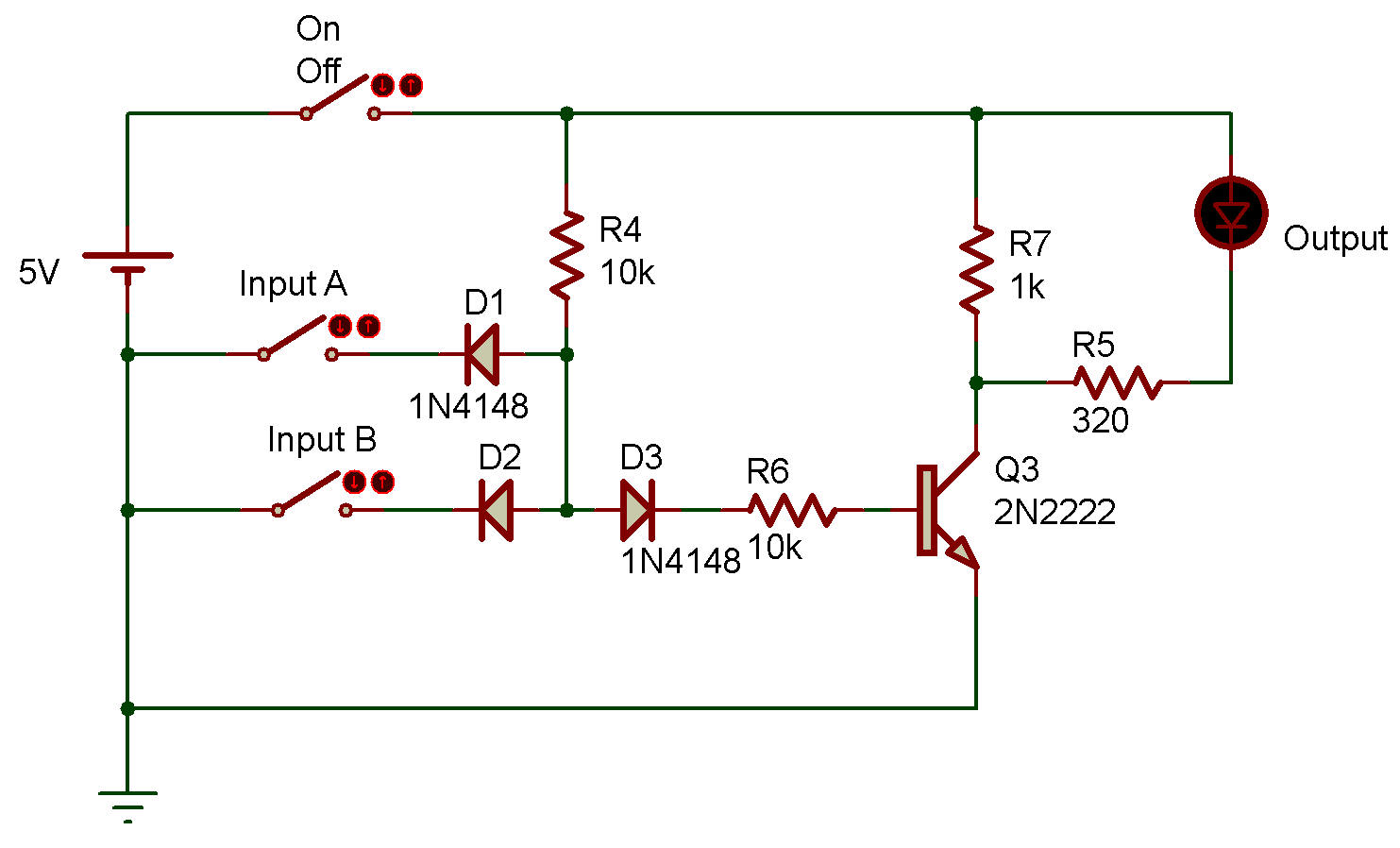

La figure 14 montre le circuit de base de l'amplificateur

numérique ECL — un amplificateur différentiel couplé à un émetteur non saturant

(Q1 et Q2) avec des étages de sortie émetteur-suiveur (Q3 et Q4).

Comme ses transistors ne saturent pas lorsqu'ils sont commutés, il donne des délais de propagation typiques de seulement 4 nS.

Notez que la ligne V+ du circuit est normalement mise à la terre et que la ligne V- est alimentée à -5,2 V.

FIGURE 14. Circuit amplificateur ECL (Emitter-Coupled Logic) de base.

Dans ces conditions, le circuit fournit des oscillations de sortie numérique nominales de seulement 0,85 V, c'est-à-dire d'un état bas de -1,60 V à un état haut de -0,75 V.

L'entrée numérique du circuit

est appliquée à la base de Q1. Une sortie non inversée est disponible sur

l'émetteur Q3, et une sortie inversée est disponible sur l'émetteur Q4. Les

circuits intégrés ECL modernes sont utilisés uniquement lorsqu'un fonctionnement

ultra-rapide est requis.

L'objectif fondamental des concepteurs de

circuits intégrés numériques de la fin des années 1960 et au début des années

1970 était de concevoir une technologie simple à utiliser et offrant un bon

compromis entre une vitesse de fonctionnement élevée et une faible consommation

d'énergie.

Le problème ici était que les circuits classiques de type transistor, utilisant un étage de sortie du type Figure 2 (comme dans les systèmes RTL et DTL), n'étaient tout simplement pas capables de répondre aux deux derniers de ces besoins de conception.

L’essence de ce problème – et

sa solution ultime – peut être comprise à l’aide de la figure 15.

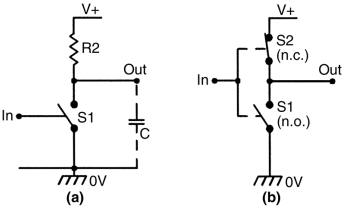

FIGURE

15. (a) Commutateur numérique simple. (b) Commutateur numérique de base

« totem ».

La figure 15 (a) montre une version simplifiée du circuit de la figure 2, avec Q1 remplacé par un interrupteur mécanique.

N'oubliez pas ici que toutes les charges de sortie pratiques contiennent inévitablement une capacité (généralement jusqu'à environ 30 pF dans la plupart des circuits numériques), on peut donc voir que ce circuit de base chargera (source de courant dans) une charge capacitive assez lentement via R2 lorsque S1 est ouvert, mais le déchargera (en absorbera le courant) rapidement via S1 lorsque S1 est fermé.

Ainsi, les circuits de ce type

produisent des sorties numériques qui ont tendance à avoir des temps de montée

longs et des temps de descente courts. La seule façon de réduire le temps de

montée est de réduire la valeur R2, ce qui augmente la consommation de courant

de S1 (Q1) d'une quantité proportionnelle.

Notez qu'une bonne façon de

décrire les défauts du circuit logique de la figure 15(a) est de dire que sa

sortie donne une action pull-down active (via S1), mais une action pull-up

passive (via S2).

Évidemment, un étage de sortie numérique bien meilleur pourrait être réalisé en remplaçant R2 et S1 par une paire de commutateurs couplés, connectés comme le montre la figure 15 (b), de sorte que S2 donne une action de traction active et S1 donne une action de traction active vers le bas, mais disposée de manière à ce qu'un seul interrupteur puisse être fermé à la fois (garantissant ainsi que le circuit ne consomme aucun courant de repos).

Un tel circuit – avec un

commutateur électronique placé au-dessus de l’autre – est appelé étage de sortie

totem.

Tout au long de la fin des années 1960, les ingénieurs numériques

se sont efforcés de concevoir une version électronique bon marché et fiable de

l’étage de sortie totem, puis, au début des années 1970, ils ont décroché le

jackpot.

Deux de ces technologies ont fait l’effet d’une bombe sur le marché commercial et sont devenues la base des deux familles de circuits intégrés numériques dominantes d’aujourd’hui. Le premier d'entre eux, basé sur la technologie des transistors bipolaires, est connu sous le nom de TTL (Transistor-Transistor Logic).

TTL est la base de la famille

dite « 74 » de circuits intégrés numériques arrivée pour la première fois en

1972.

La seconde, basée sur la technologie FET, est connue sous le nom de

CMOS (Complementary MOS-FET logic).

Le CMOS est à la base de la famille de circuits intégrés numériques rivale de la « série 4000 » (et de la famille similaire de la « série 4500 »), arrivée pour la première fois vers 1975.

Les technologies TTL et CMOS

ont des caractéristiques très différentes, mais toutes deux offrent des

avantages techniques spécifiques qui les rendent inestimables dans des

applications particulières.

Les différences les plus significatives entre

les technologies des circuits intégrés CMOS et TTL peuvent être observées dans

leurs réseaux inverseurs/tampon de base, qui sont utilisés (parfois sous une

forme légèrement modifiée) dans pratiquement tous les circuits intégrés de la

gamme de chaque type d'appareil.

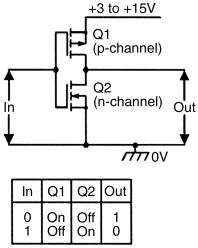

Les figures 16 et 17 montrent les deux conceptions de base différentes.

FIGURE 16. Circuit et table de vérité d'un inverseur CMOS de base.

L'inverseur CMOS de la

figure 16 se compose d'une paire complémentaire de MOSFET, câblés en série, avec

un MOSFET Q1 à canal P en haut et un MOSFET Q2 à canal N en dessous, et avec les

deux portes haute impédance réunies. La paire peut être alimentée à partir de

n’importe quelle alimentation dans la plage 3 à 15 V.

Lorsque l'entrée du circuit est au niveau logique 0, l'action de base est telle que Q1 est activé et Q2 est coupé, et la sortie est activement tirée vers le haut (vers le niveau logique 1).

Notez que la sortie peut

générer (entraîner) des courants assez élevés dans une charge externe (via Q1)

dans cette condition, mais que l'étage inverseur réel consomme un courant proche

de zéro, puisque Q2 est coupé.

Lorsque l'entrée du circuit est au niveau

logique 1, l'inverse de cette action se produit : Q1 est coupé et Q2 est activé,

et la sortie est activement tirée vers le bas (vers le niveau logique 0).

Notez que la sortie peut

absorber (absorber) des courants assez élevés provenant d'une charge externe

(via Q2) dans cette condition, mais que l'étage inverseur réel consomme un

courant proche de zéro, puisque Q1 est coupé.

Ainsi, l'onduleur CMOS de

base peut être utilisé avec n'importe quelle alimentation dans la plage 3-15 V,

possède une impédance d'entrée très élevée, consomme un courant de repos proche

de zéro, possède une sortie qui commute presque entièrement entre les deux rails

d'alimentation et peut fournir ou absorber des courants de charge de sortie

assez élevés.

Généralement, un seul étage

CMOS de base a un retard de propagation d'environ 12 à 60 nS, en fonction de la

tension d'alimentation.

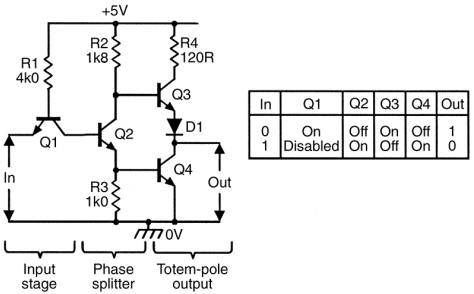

L'onduleur TTL de la figure 17 est divisé en

trois sections, constituées d'une entrée pilotée par un émetteur (Q1), d'un

séparateur de phase (Q2) et d'un étage de sortie totem (Q3-D1-Q4).

Il doit être alimenté par une alimentation de 5 volts.

Lorsque l'entrée du circuit est

ramenée à 0 logique, l'action de base est telle que Q1 est saturé, privant ainsi

Q2 de courant de base et provoquant la coupure de Q2 et Q4, et, en même temps,

provoquant la coupure de l'émetteur-suiveur Q3 allumez via R2 et donne une

action de rappel active dans laquelle la sortie a (en raison de diverses chutes

de tension) une valeur chargée typique d'environ 3,5 V.

FIGURE 17.

Circuit et tableau de vérité d'un onduleur TTL de base.

Ce circuit peut générer des

courants assez élevés dans une charge externe. À l’inverse, lorsque l’entrée du

circuit est au niveau logique 1, Q1 est désactivé, permettant à Q2 d’être activé

via R1 et la jonction base-collecteur polarisée en direct de Q1, conduisant

ainsi Q4 à saturation et coupant simultanément Q3.

Dans ces conditions,

Q4 donne une action pull-down active et peut absorber des courants assez élevés,

tandis que la sortie prend une valeur chargée typique de 400 mV.

Notez que (en ignorant les

courants de charge externes), le circuit consomme un courant de repos d'environ

1 mA dans l'état de sortie logique 1 et 3 mA dans l'état de sortie logique 0.

Ainsi, l'onduleur TTL de base ne peut être utilisé qu'avec une alimentation

de 5 volts, a une très faible impédance d'entrée, consomme jusqu'à 3 mA de

courant de repos, a une sortie qui ne commute pas complètement entre les deux

rails d'alimentation et peut fournir ou absorber des courants de charge assez

élevés.

Généralement, un seul étage TTL de base a un retard de propagation d'environ 12 nS.

VARIATIONS DE BASE DU CIRCUIT TTL

Il existe cinq variantes très importantes du circuit inverseur TTL de base de la figure 17.

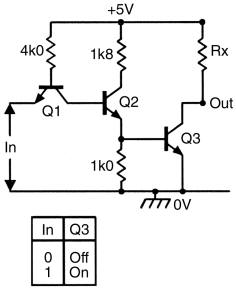

Le plus simple d'entre eux est le circuit TTL dit « à collecteur ouvert », qui est illustré en schéma de base à la figure 18.

FIGURE 18. Onduleur TTL avec sortie à collecteur ouvert.

Ici, le transistor de sortie Q3 est coupé lorsque l'entrée est à 0 logique et est rendu passant lorsque l'entrée est à 1 logique.

Ainsi, en câblant une

résistance de charge externe entre les broches OUT et +5 V, le circuit peut être

utilisé comme un onduleur de tension de rappel passif doté d'une sortie qui

(lorsqu'elle est légèrement chargée) commute presque entièrement entre zéro et

le rail d'alimentation positif.

Alternativement, il peut être utilisé

pour piloter une charge externe (telle qu'une LED ou un relais, etc.) connectée

entre OUT et un rail d'alimentation positif, auquel cas la charge s'active

lorsqu'une entrée logique 1 est appliquée.

La deuxième variante est

l’amplificateur ou tampon non inverseur. Ceci est réalisé en câblant simplement

un étage inverseur supplémentaire à couplage direct entre le séparateur de phase

et les étages de sortie de l'onduleur standard.

La figure 19 montre une version à collecteur ouvert d'un tel circuit, qui peut être utilisée avec une résistance ou une charge externe. Dans cet exemple, Q4 s'allume lorsqu'une entrée logique 0 est appliquée.

FIGURE 19. Tampon non inverseur TTL avec sortie à collecteur ouvert.

La figure 20 montre une variation majeure de conception TTL.

FIGURE 20. Porte NAND TTL à trois entrées.

Ici, le circuit inverseur de base est utilisé avec un transistor d'entrée à triple émetteur, pour créer une porte NAND à trois entrées dans laquelle la sortie passe au niveau bas (à 0 logique) uniquement lorsque les trois entrées sont hautes (dans l'état logique 1).

Les transistors à émetteurs

multiples sont largement utilisés dans les circuits intégrés TTL. Certaines

portes TTL utilisent un transistor d'entrée avec jusqu'à une douzaine

d'émetteurs pour créer une porte à 12 entrées.

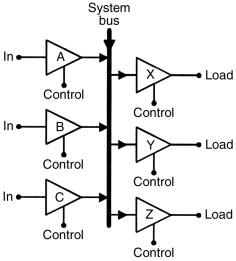

Une autre variante

concerne l'utilisation d'une sortie de type « Tri-State » (ou « trois états »)

qui intègre des réseaux supplémentaires ainsi qu'un terminal de contrôle ENABLE

externe.

Dans un état, l'étage de sortie totem-pôle fonctionne dans son mode logique 0 ou logique 1 normal, mais dans l'autre état, les deux transistors totem-pôle sont désactivés (éteints), créant un circuit ouvert (haute impédance) sortir.

Cette fonctionnalité est utile

pour permettre à plusieurs sorties ou entrées d'être court-circuitées vers un

bus ou une ligne commune, comme le montre la figure 21, et de communiquer le

long de cette ligne en ACTIVANT une seule sortie et un seul périphérique

d'entrée à la fois.

FIGURE 21. La logique à trois états permet de

connecter plusieurs sorties ou entrées à un bus commun. Une seule sortie/entrée

doit être rendue active à un moment donné.

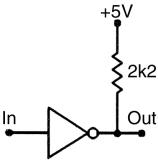

La variante du circuit final

est une variante d'application et concerne l'utilisation d'une résistance de

rappel externe de 2 kΩ sur un étage de sortie totem-pôle, comme le montre la

figure 22.

FIGURE 22. Une résistance de rappel externe de 2 kW connectée

à la sortie d'un étage totem-pôle tire la sortie à presque +5 V dans l'état

logique 1.

Cette résistance tire la sortie (lorsqu'elle est légèrement chargée) jusqu'à

pratiquement la pleine valeur d'alimentation de +5 V lorsque la sortie est dans

l'état logique 1, plutôt qu'à seulement +3,5 V.

Ceci est parfois utile lors de l'interface avec la sortie d'un IC TTL à l’entrée d’un IC CMOS, par exemple.

LE SCI NUMÉRIQUE « SÉRIE 74 »

La technologie des circuits intégrés TTL a fait son apparition sur la scène de l'ingénierie électronique vers 1972, lorsqu'elle est arrivée sous la forme d'une gamme complète de circuits intégrés logiques numériques exceptionnellement faciles à utiliser.

La gamme a connu un succès international instantané et est rapidement devenue le système logique IC leader au monde.

Ses circuits intégrés étaient

produits à la fois dans des qualités commerciales et militaires et portaient

respectivement les préfixes 74 et 54 ; la gamme de produits commerciaux est

rapidement devenue simplement connue sous le nom de CI « série 74 ».

Au

fil des années, les circuits intégrés de la « série 74 » ont progressivement

élargi leur gamme de dispositifs et amélioré leur technologie de production, de

sorte qu'aujourd'hui la série 74 est aussi populaire et polyvalente que jamais.

Lors de son introduction au début des années 1970, la série était entièrement basée sur un type simple de technologie TTL, mais au cours des années suivantes, de nouvelles sous-familles de TTL ont été introduites dans la série, puis divers types de technologie CMOS y ont été ajoutés.

De sorte que la série 74 actuelle intègre une variété de sous-familles TTL et CMOS. Notre prochain section examinera de près les sous-familles de circuits intégrés de la série 74 et expliquera une terminologie de base TTL.

| Famille TTL | Sous-famille | Délai (nS) | Vcc (V) |

| Basic | 10 | 5 | |

| Low-power | L | 60 | 5 |

| Schottky | S | 20 | 5 |

| Low-power Schottky | LS | 15 | 5 |

| Advanced Schottky | AS | 4.5 | 5 |

| Advanced Low-Power Schottky | ALS | 11 | 5 |

| CMOS | C | 60 | 3-15 |

| High-Speed | H | 10 | 5 |

| High-Speed CMOS | HC | 15 | 2-6 |

| High-Speed CMOS | HCT | 15 | 5 |

|

Schmitt-Trigger Integrated High-Speed CMOS |

HCS | 13 | 2-6 |

| Fast | F | 3.9 | 5 |

Conditions de fonctionnement

(+25°C) IC4011

Operating Conditions (+25°C) IC4011

Symbole

Symbol

Paramètre

Parameter

Conditions

Minimum

Typique

Typical

Maximum

Unités

Units

Vcc

Tension d'alimentation

Supply Voltage

3

15

V

VIH

Tension d'entrée de niveau élevé

HIGH Level Input Voltage

Vdd=5V,Vo= 0.5 V

Vdd=10V,Vo=1.0V

Vdd= 15V, Vo= 1.5V

3.5

7.0

11.0

3

6

9

V

VlL

Tension d'entrée de niveau FAIBLE

LOW Level Input Voltage

Vdd=5V, Vo=4.5V

Vdd=10V,Vo=9.0 V

Vdd=15V, Vo=13.5V

2

4

6

1.5

3.0

4.0

V

VOH

Tension de sortie de haut niveau

HIGH Level Output Voltage

Vdd=5 V

Vdd=10V

Vdd= 15V

4.95

9.95

14.95

5

10

15

VOL

Tension de sortie de niveau FAIBLE

LOW Level Output Voltage

Vdd =5V

Vdd=10V

Vdd = 15V

0

0

0

0.05

0.05

0.05

IOH

Courant de sortie de haut niveau

HIGH Level Output Current

Vdd=5V,Vo=4.6V

Vdd=10V,Vo=9.5 V

Vdd= 15V, Vo=13.5V

-0.44

-1.1

-3.0

-0.88

-2.25

-8.8

mA

IOL

Courant de sortie de niveau FAIBLE

LOW Level Output Current

Vdd=5V, Vo=0.4V

Vdd=10V,Vo=0.5V

Vdd=15V, Vo=1.5V

0.44

1.1

3.0

0.88

2.25

8.8

mA

TA

Température de fonctionnement

à l'air libre

Free Air Operating

Temperature

-40

-85

°C