Les Portes logiques

Les tampon numérique, les portes logiques et les IC logiques

Symbologie

Les huit types de portes logiques numériques les plus connus sont le tampon et les types NOT, OR, NOR, AND, NAND, XOR (EX-OR) et XNOR (EX-NOR).

De nombreux symboles différents peuvent être utilisés pour représenter chacun de ces huit éléments de porte logique de base.

Il existe quatre familles différentes de symboles qui sont aujourd’hui largement utilisés dans différentes parties du monde.

Parmi ceux-ci, les symboles américains MIL/ANSI sont de loin les plus populaires, sont immédiatement reconnaissables, sont utilisés par la plupart des ingénieurs numériques pratiques du monde et sont utilisés tout au long de cette série.

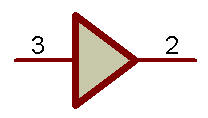

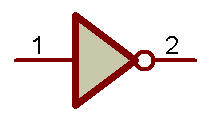

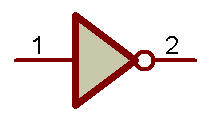

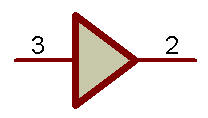

La figure ci-dessous montre les symboles américains MIL/ANSI

Buffer / Tampon |

Inverter / Inverseur(NOT) |

|

2-input OR gate / Porte OU à 2

entrées |

2-i n put NOR gate / Porte NON-OU à 2

entrées |

|

2-input AND gate / Porte ET à 2

entrées |

2-inpul NAND gale / Porte NON-ET à 2

entrées |

|

2-input EX-OR gate / Porte EX-OR à 2

entrées |

2-input EX-NOR gate / Porte EX-NOR à

2 entrées |

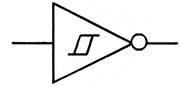

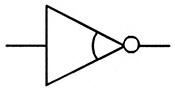

Deux variantes utiles de ces symboles américains sont également largement utilisées et sont présentées ajoutées à un symbole d'onduleur standard sur la figure ci-dessous:

Ce symbole est internationalement reconnu et indique que l'élément logique a une action d'entrée de déclenchement de Schmitt.

le symbole ci-dessous — qui est largement utilisé mais n'est pas universellement reconnu — indique que l'élément logique possède un étage de sortie à collecteur drain (o.d.) ou à collecteur ouvert (o.c.).

Fonctions des portes logiques

L'action fonctionnelle de toute porte logique peut être décrite soit par des

mots, soit sous forme de tableau ou symbolique. La liste suivante décrit en mots

les fonctions des huit types de base de portes logiques.

Tampons — Un

tampon est un amplificateur non inverseur qui a une capacité de commande de

sortie qui est bien supérieure à ses exigences en matière de commande d'entrée,

c'est-à-dire qu'il a une sortance élevée et donne une sortie logique 1 pour une

entrée logique 1, etc.

Inverseur (NOT) — Un inverseur, également connu sous le nom de porte NON, (NOT), est un ampli à sortance élevée qui donne une sortie logique 1 pour une entrée logique 0, et vice versa.

Portes OU (OR) — Une porte OU a une sortie qui va à la logique 1 si une entrée est à la logique 1, c'est-à-dire si les entrées A, B ou C, etc., sont élevées. La sortie passe au 0 logique uniquement si toutes les entrées sont au 0 logique.

Portes NON-OU (NOR) — Une porte NOR est une porte OU avec une sortie inversée ; elle a une sortie qui passe au 0 logique si une entrée est au 1 logique, et passe au 1 logique uniquement lorsque toutes les entrées sont au 0 logique.

Portes ET (AND)— Une porte ET a une sortie qui est normalement au niveau logique 0 et ne passe au niveau logique 1 que lorsque toutes les entrées sont au niveau logique 1, c'est-à-dire lorsque les entrées A, B et C, etc., sont au niveau haut.

Portes NON-ET (NAND) — Une porte NAND est une porte ET avec une sortie inversée (inversée) ; la sortie est normalement au logique 1 et ne passe au logique 0 que lorsque toutes les entrées sont au logique 1.

Portes XOR — Une porte OU exclusif (EX-OR) a deux entrées et sa sortie passe au logique 1 uniquement si une seule entrée (A ou B) est au logique 1 ; la sortie passe au 0 logique si les deux entrées sont dans le même état logique.

Portes XNOR — Une porte EX-NOR (EX-NOR) est une porte EX-OR avec une sortie inversée, qui passe au logique 1 si les deux entrées sont dans le même état logique, et passe au logique 0 uniquement si une seule entrée est en logique 1.

Le tableau Portes Logiques Table de Vérité montre comment les fonctions des huit types de portes de base peuvent également être présentées sous forme de tableau via des tables de vérité (qui montrent l'état logique de la sortie pour toutes les combinaisons possibles d'états logiques d'entrée) ou symboliquement via des termes algébriques booléens.

Notez que, par convention, toutes les entrées de porte logique sont notées par ordre alphabétique comme A, B, C, etc., et la borne de sortie est notée Y (dans les compteurs et les i-pops, etc., la sortie principale est généralement notée Q).

Les états logiques réels peuvent être représentés par 0 et 1, comme indiqué, ou par L (= niveau logique bas) et H (= niveau logique haut).

Notez également dans les expressions booléennes qu'une sortie annulée est indiquée par une barre de négation dessinée au-dessus du symbole de sortie de base ; l’état nié est appelé un état non ; ainsi, une sortie Y annulée est appelée une sortie non-Y.

|

Portes Logiques Table de Vérité |

|||||||||||||||||||||||||||||||

|

Tampon Buffer

|

Porte NON (Inverseur) NOT Gate (Inverter)

|

||||||||||||||||||||||||||||||

|

Porte OU OR Gate

|

Porte NON OU NOR Gate

|

||||||||||||||||||||||||||||||

|

Porte ET AND Gate

|

Porte NON ET NAND Gate

|

||||||||||||||||||||||||||||||

|

Porte XOR XOR Gate

|

Porte XNOR XNOR Gate

|

||||||||||||||||||||||||||||||

Logique positive versus négative

Tous les circuits logiques numériques modernes supposent l'utilisation de la convention de logique positive, dans laquelle un état logique 1 est haut et un état logique 0 est bas.

Aux débuts des circuits électroniques numériques, une convention alternative de « logique négative » — dans laquelle un état logique 1 est bas et un état logique 0 est haut — était également couramment utilisée, et il est parfois encore utile de pouvoir penser en termes de logique négative, en particulier lors de la conception de portes dans lesquelles une sortie à état bas présente un intérêt particulier.

Ainsi une action de porte ET logique négative - dans laquelle la sortie est basse uniquement lorsque les deux entrées sont basses - est directement disponible à partir d'une porte OU logique positive, et ainsi de suite.

Circuits tampons pratiques

Les circuits intégrés tampons numériques ont deux objectifs principaux : agir soit comme de simples interfaces non inverseuses augmentant le courant entre une partie d'un circuit et une autre, soit comme des unités de commutation à trois états pouvant être utilisées pour connecter les sorties d'un circuit à une charge, seulement lorsque cela est nécessaire.

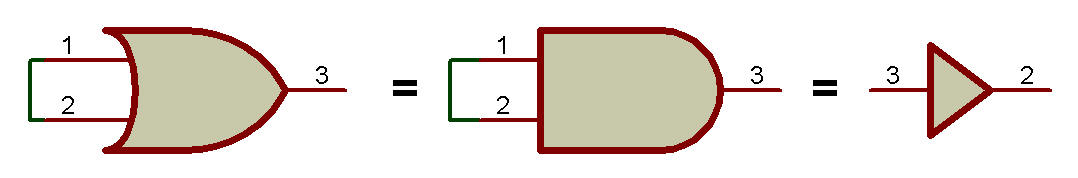

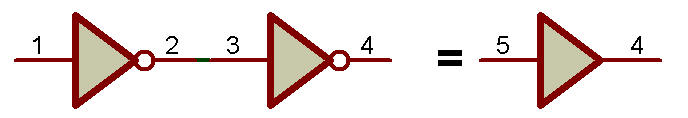

Si jamais vous n'avez besoin que de quelques tampons simples, un moyen peu coûteux de les obtenir est de les fabriquer à partir d'éléments AND ou OR de rechange (comme le montre la figure) ou de paires d'inverseurs normaux ou Schmitt.

Paires d'inverseurs

La tableau répertorie les détails de base de neuf circuits intégrés tampons numériques non inverseurs populaires.

| IC | Type | Description |

| 74LS125 | LS | QUAD 3-state buffer |

| 4050 | CMOS | Hex buffer |

| 4503B | CMOS | Hex (Dual Quad) 3-state buffer |

| 7407 | TTL | Hex buffer with 30V o.c. outputs |

| 74LS365 | LS | Hex 3-state buffer |

| 74HC4050 | CMOS | Hex buffer |

| 74HC241 | CMOS | Octal (Dual Quad) 3-state Schmitt buffer |

| 74HC244 | CMOS | Octal (Dual Quad) 3-state Schmitt buffer |

| 74LS244 | LS | Octal (Dual Quad) 3-state Schmitt buffer |

Lors de l'utilisation de ces circuits intégrés, notez que tous les tampons inutilisés doivent être désactivés en reliant leurs entrées à l'une des lignes d'alimentation du circuit intégré.

Dans les appareils CMOS, les entrées inutilisées peuvent être reliées directement à l'une ou l'autre ligne d'alimentation, mais dans les appareils TTL, il est préférable (pour une consommation de courant de repos la plus faible) de lier toutes les entrées inutilisées à un niveau élevé via une résistance commune de 10K.

Si le tampon inutilisé est de type à trois états, il doit (s'il dispose d'un contrôle indépendant) être mis en mode normal via son entrée de contrôle.

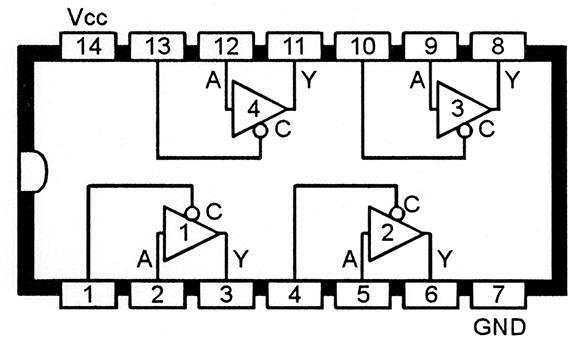

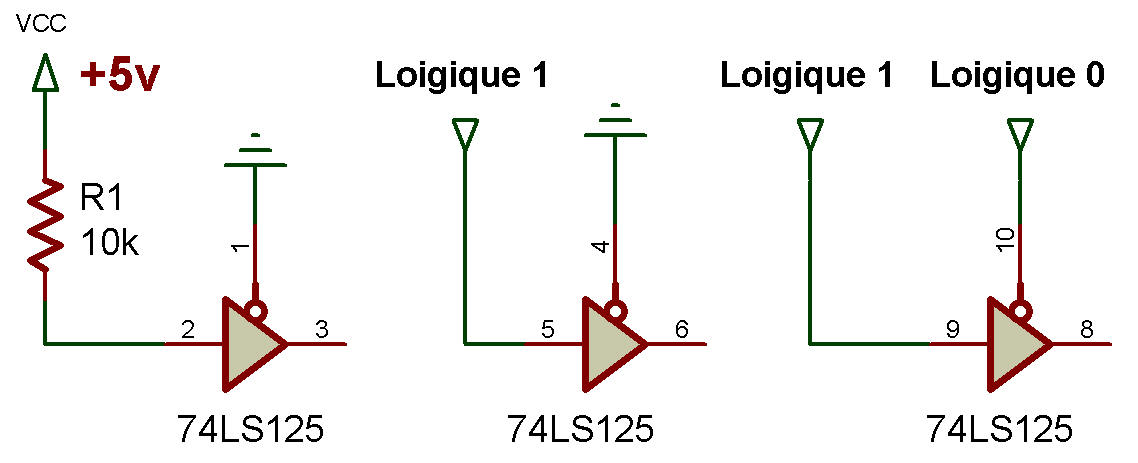

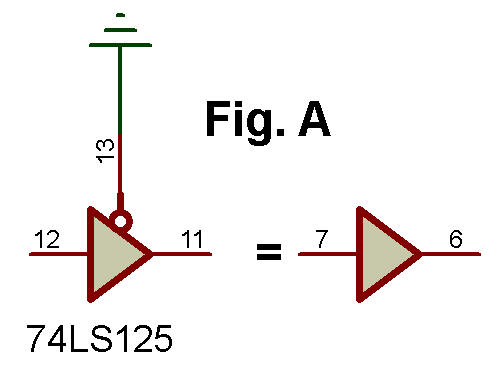

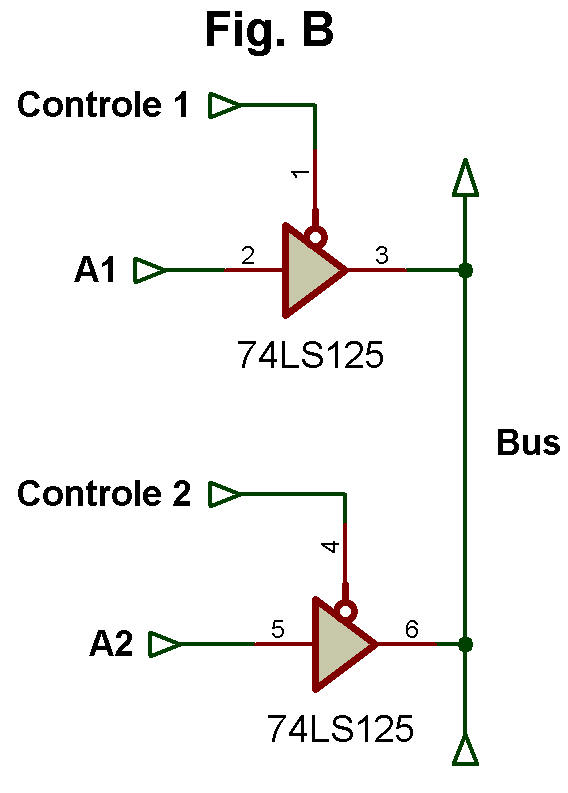

La figure ci-dessous montre le schéma fonctionnel et la table de vérité du circuit intégré TTL 74LS125, qui héberge quatre tampons à trois états contrôlés indépendamment et dont le prix est si modeste qu'il vaut toujours la peine de l'utiliser, même si vous n'avez pas besoin de l'installation à trois états.

Voir Aussi 74LS125

| C | A | Y | Is par porte |

| 0 | 0 | 0 | 2.25 mA |

| 0 | 1 | 1 | 1.12 mA |

| 1 | 1 | Hi-Z | 2.75 mA |

| 1 | 1 | Hi-Z | 2.62 mA |

| Diffusion par défaut = 30 | |||

Notez dans la table de vérité que chacun des quatre éléments agit comme un tampon normal lorsque sa borne de commande (C) est à l'état logique 0, et que le courant de repos de l'élément (Is) est moindre lorsque C est à 0 logique et que le courant de repos du tampon l'entrée (A) est à 1 logique.

Ainsi, tous les éléments inutilisés doivent être désactivés en attachant leurs bornes C au niveau bas et leurs bornes A au niveau haut, en utilisant l'une des méthodes illustrées dans la figure.

Tous les éléments 74LS125 inutilisés doivent être connectés de l'une de ces manières.

Tout élément peut être utilisé comme tampon normal en mettant à la terre sa borne C (Figure A), ou comme tampon à trois états qui pilote une ligne de bus commune en l'utilisant comme le montre la figure B.

|

|

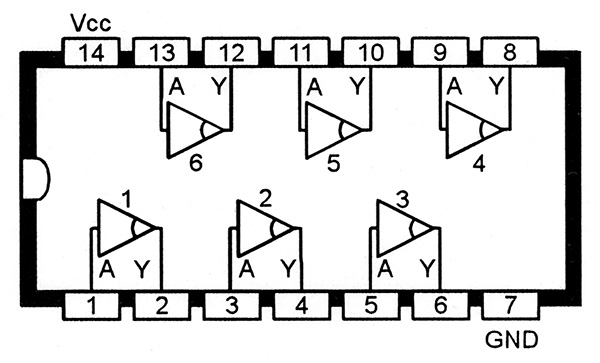

Si vous avez besoin jusqu'à six tampons CMOS simples, l'un des moyens les moins chers de les obtenir consiste à utiliser un circuit intégré de tampon hexadécimal 4050B ou 74HC4050.

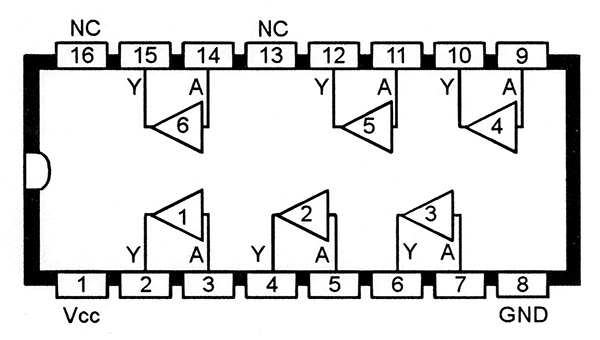

La figure montre le schéma fonctionnel du IC ; chaque tampon peut fournir jusqu'à 10 mA ou absorber jusqu'à 40 mA de courant de sortie lorsque le circuit intégré est alimenté par une alimentation de 15 V.

Schéma fonctionnel du circuit intégré tampon hexadécimal 4050B ou 74HC4050

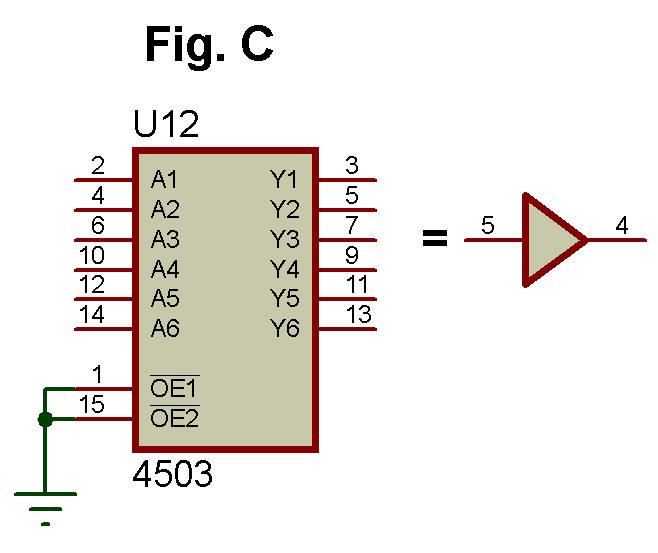

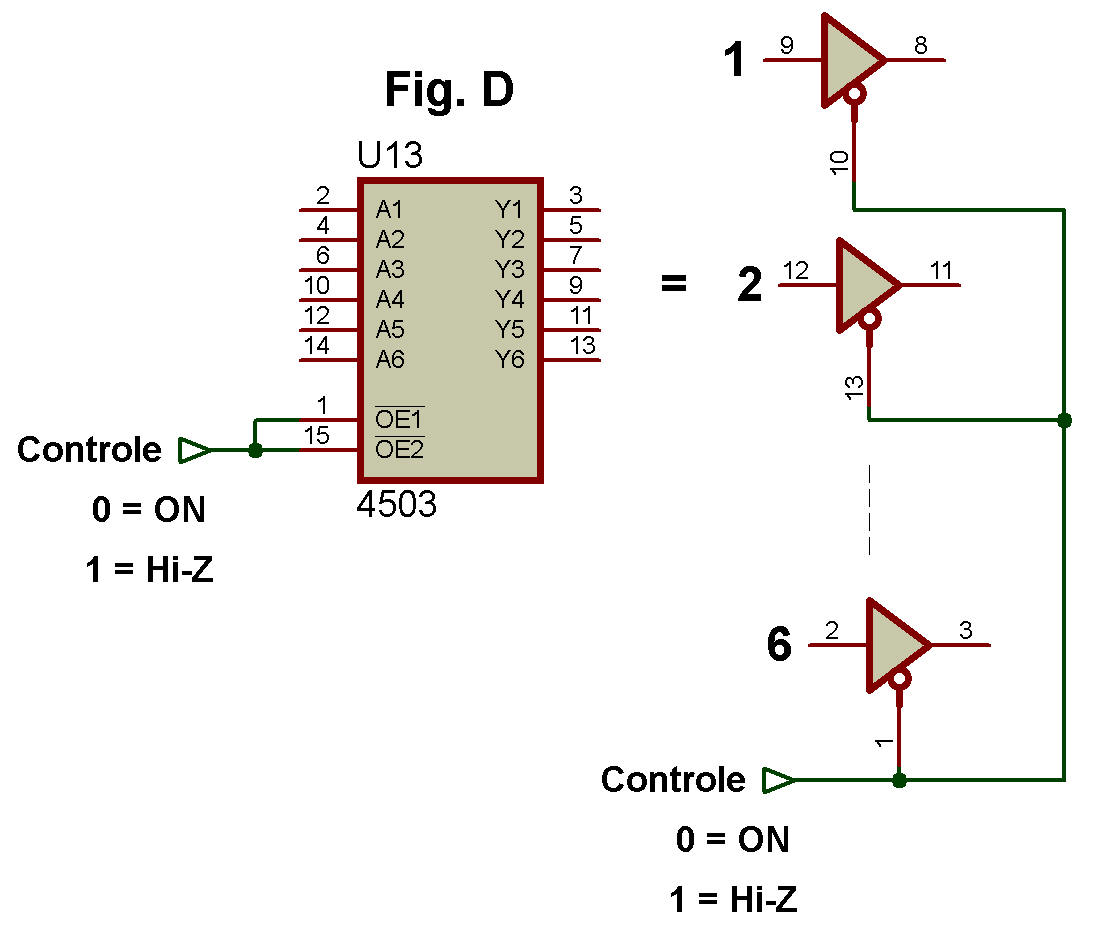

Si vous avez besoin de jusqu'à six tampons CMOS à trois états, une option consiste à utiliser un circuit intégré tampon hexadécimal 4503B.

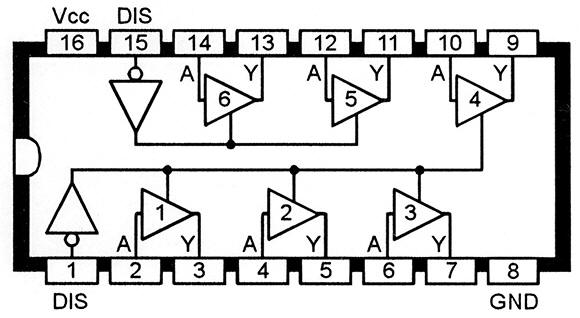

Les figure ci-dessous montre le schéma fonctionnel et la table de vérité de ce circuit intégré polyvalent, dans lequel la broche 1 agit comme une entrée DÉSACTIVÉE qui contrôle quatre des six tampons, et la broche 15 agit comme une entrée DÉSACTIVÉE qui contrôle les deux autres tampons.

Notez que chaque élément tampon agit comme un tampon normal lorsque sa broche DISABLE est à la logique 0 (faible) et passe à l'état de sortie haute impédance lorsque sa broche DISABLE est à la logique 1 (haute).

Schéma fonctionnel et table de vérité du circuit intégré tampon hexadécimal 4503B.

| In-A |

Disable Input |

Out -y |

| 0 | 0 | 0 |

| 1 | 0 | 1 |

| X | 1 | Hi-Z |

Ainsi, ce circuit intégré peut être utilisé comme un simple tampon hexadécimal en le câblant comme indiqué sur la figure C (avec les broches 1 et 15 mises à la terre), ou comme un tampon hexadécimal à trois états contrôlé via une seule entrée en le câblant comme indiqué dans Figure D (avec les broches 1 et 15 court-circuitées ensemble et utilisées comme entrée DÉSACTIVÉE).

|

|

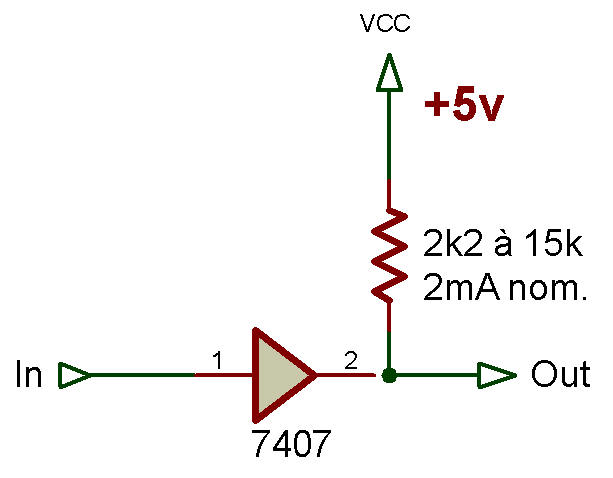

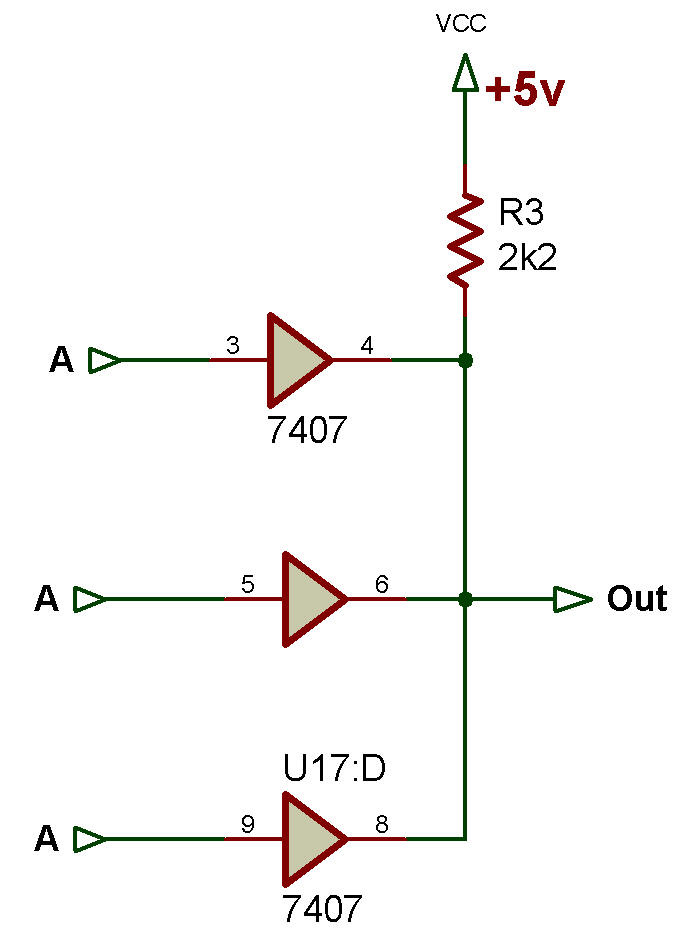

La figure ci-dessous montre le schéma fonctionnel du 7407, qui est un tampon Hex TTL standard dans lequel chaque tampon a une sortie à collecteur ouvert qui peut absorber jusqu'à 40 mA et peut être connecté à une alimentation allant jusqu'à 30 V via un courant externe de la résistance de rappel limitante (mais le circuit intégré réel doit utiliser une alimentation de 5 V).

Schéma fonctionnel du tampon Hex 7407 avec sorties collecteur ouvert 30 V.

La figure Cidessous montre comment l'un de ces tampons peut être utilisé comme interface non inverseuse de 5 V à haute tension (jusqu'à 30 V).

La figure ci-dessous montre comment trois tampons peuvent être configurés pour agir comme une porte ET câblée en câblant les trois sorties à la même résistance de rappel. L'action du circuit est telle que la sortie est abaissée lorsqu'une entrée est basse, et ne passe à l'état haut que lorsque les trois entrées sont hautes, donnant ainsi une action ET.

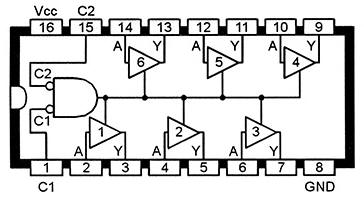

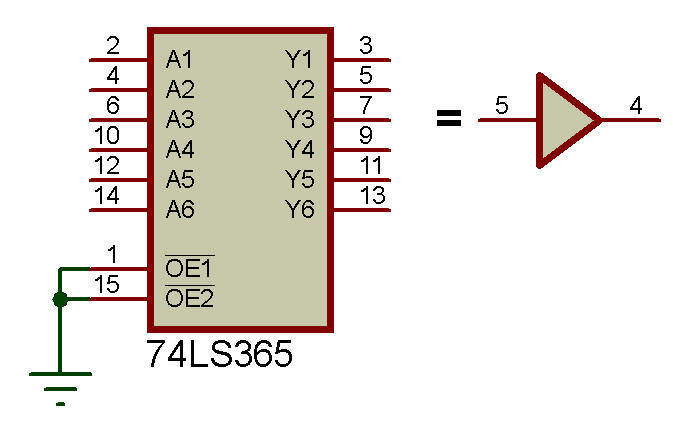

La figure ci-dessous montre le schéma fonctionnel et la table de vérité de base d'un circuit intégré tampon à trois états 74LS365 Hex, dans lequel les six tampons partagent une ligne de commande commune à porte ET.

| C1 | C2 | A | Y |

| 1 | X | X | Hi-Z |

| X | 1 | X | Hi-Z |

| 0 | 0 | 1 | 1 |

| 0 | 0 | 0 | 0 |

Ce circuit intégré peut être utilisé comme six tampons normaux en mettant à la terre ses deux broches de commande comme le montre la figure ci-dessous.

Méthodes de connexion du 74LS365 pour une utilisation comme six tampons normaux.

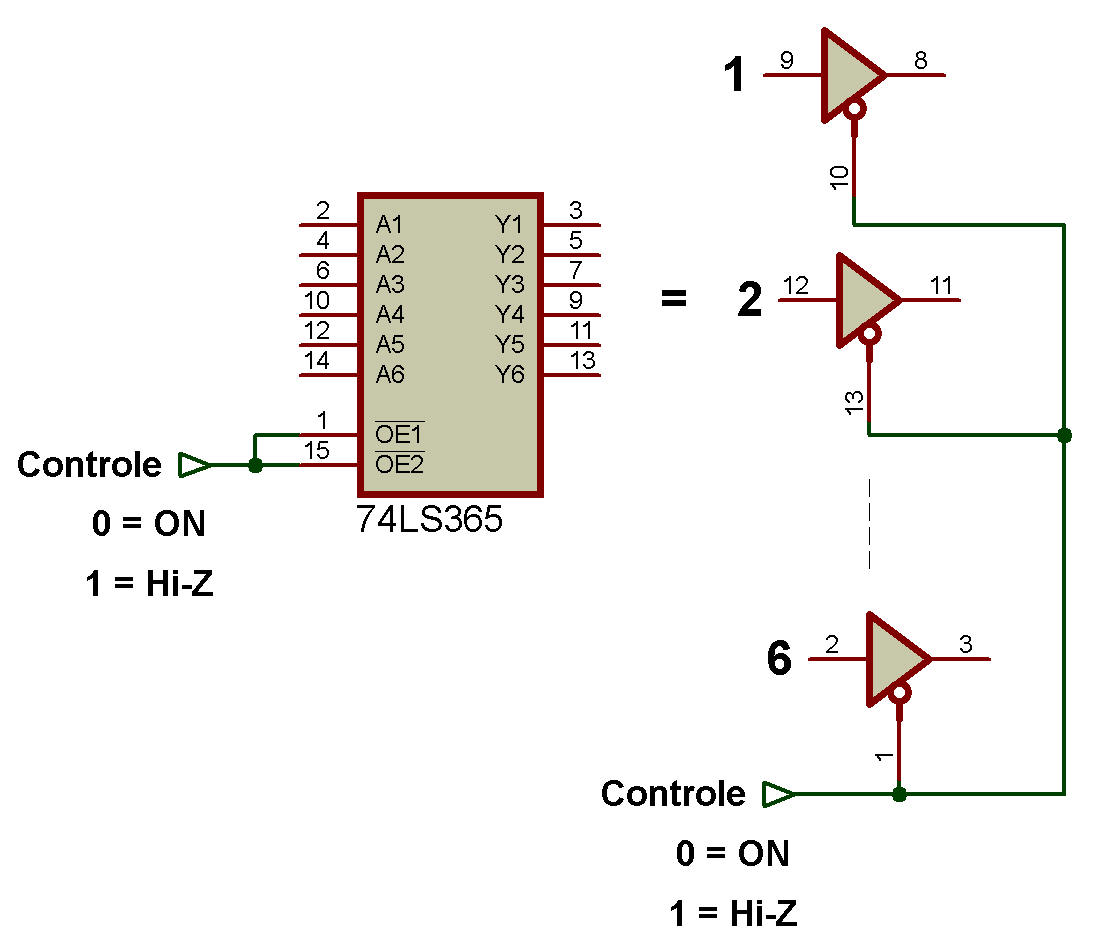

Ou comme un ensemble de six tampons à trois états qui sont tous commutés via un signal de commande commun comme le montre la figure 21 ; Un contrôle à trois états de type ET peut être obtenu en utilisant les deux bornes de contrôle (broches 1 et 15).

Méthodes de connexion du 74LS365 pour une utilisation comme tampon hexadécimal à trois états contrôlé via une seule entrée.

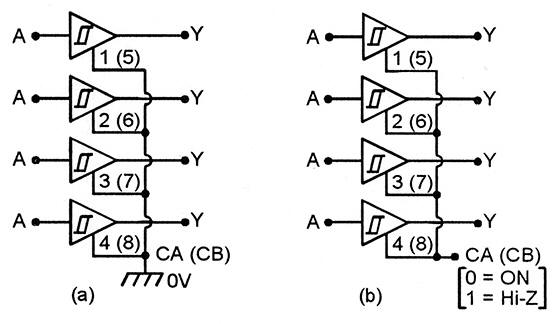

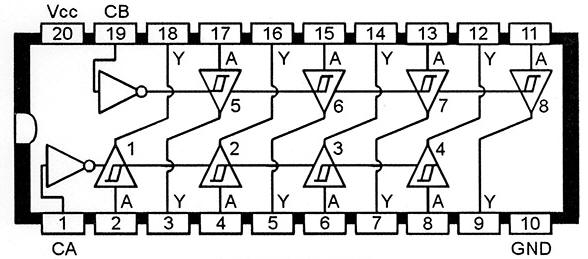

Enfin, les 74HC241, 74HC244 et 74LS244 sont des tampons Schmitt « octaux » à trois états dans lesquels les tampons sont divisés en deux groupes de quatre, le mode de chaque groupe étant contrôlé via une entrée séparée.

La figure ci-dessous montre le schéma fonctionnel et la table de vérité du CI 74LS244 (le 74HC244 est similaire, mais il possède des entrées CA et CB de type Schmitt).

Schéma fonctionnel et table de vérité du circuit intégré tampon Schmitt à trois états octal (double quad) 74LS244 (ou 74HC244).

| C1 | A | Y |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | Hi-Z |

| 1 | 1 | Hi-Z |

Le CI est en réalité un dispositif double Quad, dans lequel les tampons 1 à 4 sont contrôlés via le terminal CA et les tampons 5 à 8 sont contrôlés via les terminaux CB.

Chacun de ces quads peut être utilisé comme un ensemble de tampons Schmitt simples en mettant à la terre son terminal de contrôle comme le montre la figure (a) ci-dessous , ou comme un ensemble groupé de tampons Schmitt à trois états en utilisant son terminal de contrôle comme le montre la figure (b).