Logique ET à affichage DEL

Électronique /

Electronic

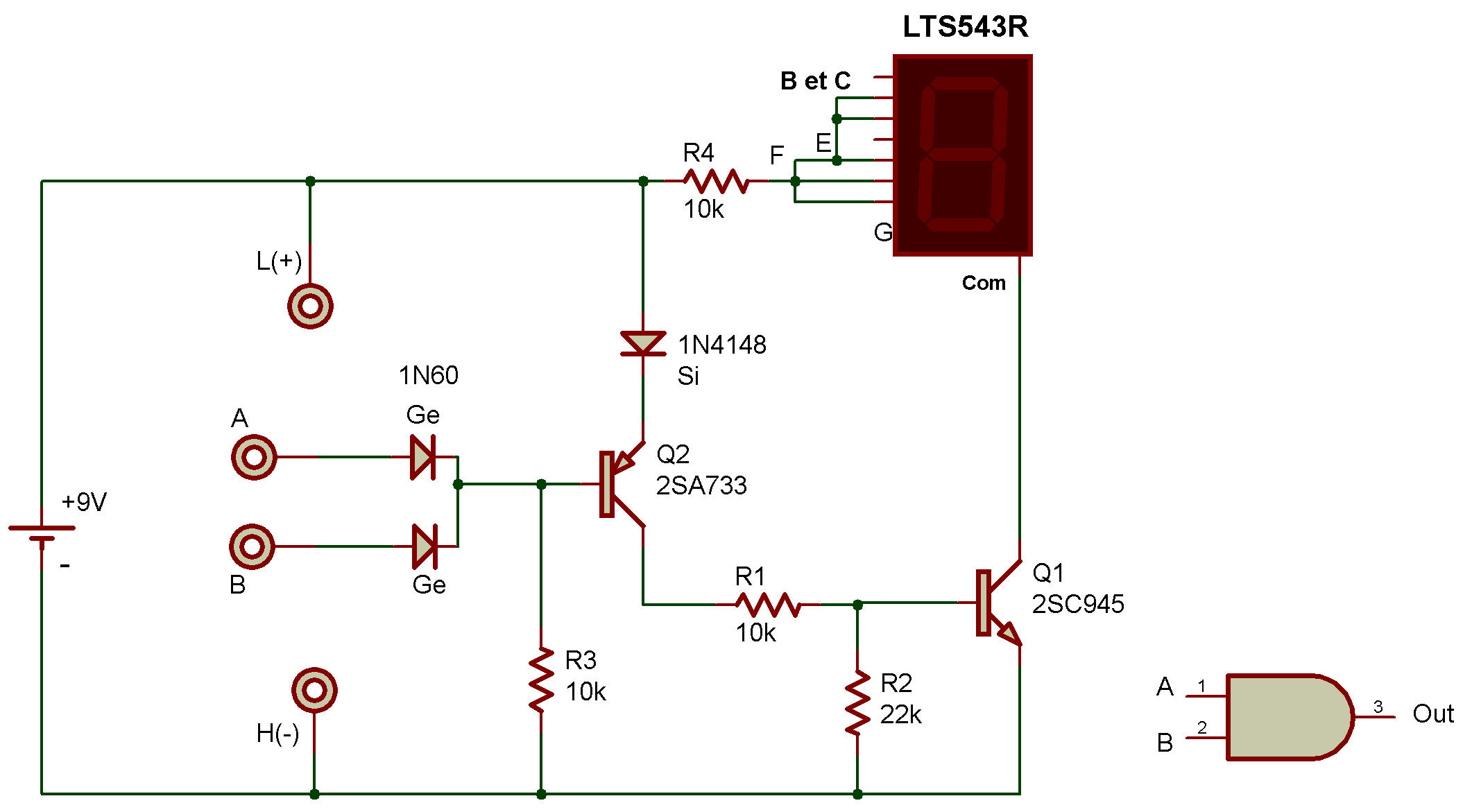

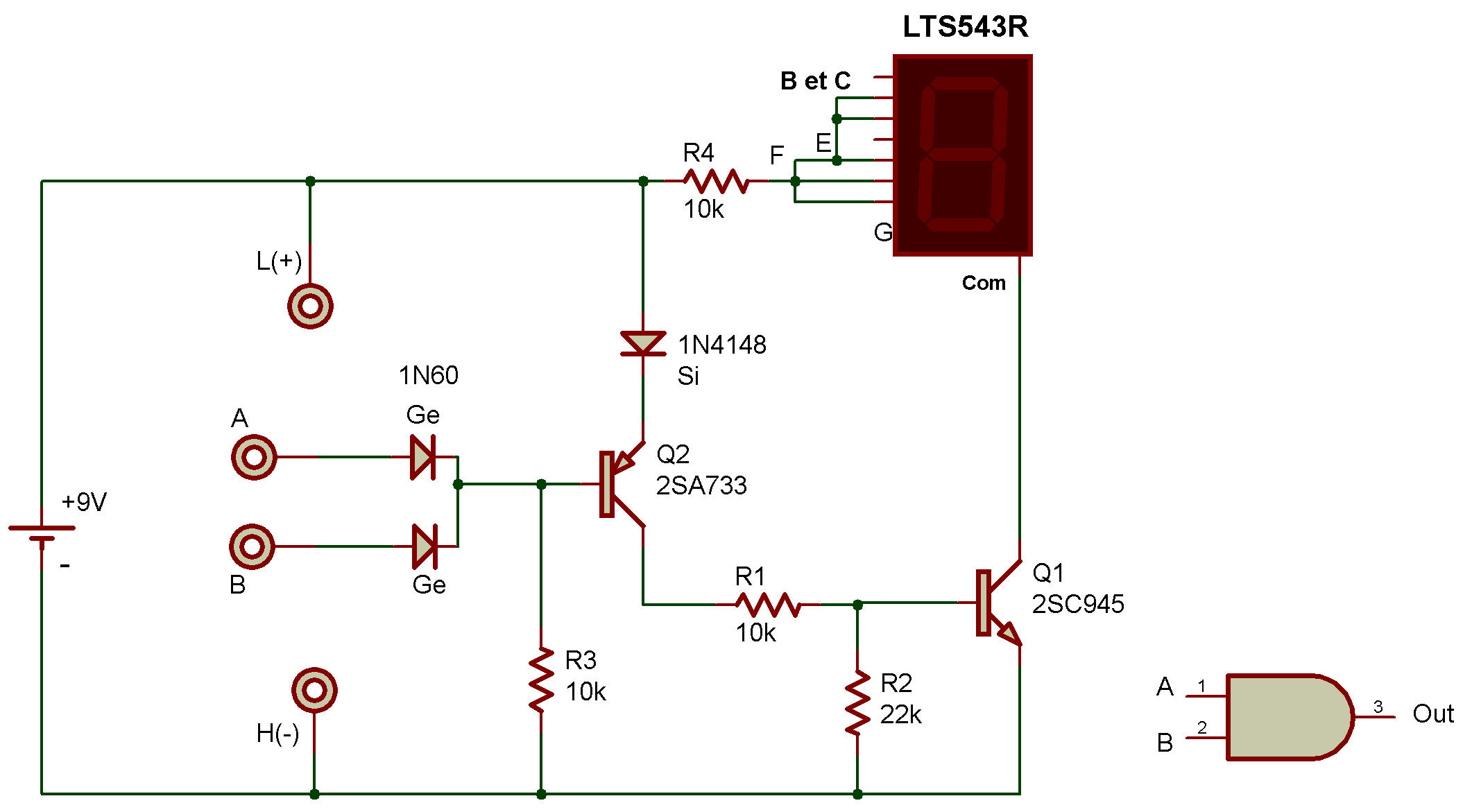

Le but de ce projet est d'étudier le circuit logique ET tel qu'utilisé pour les ordinateurs.

Le tableau est connecté pour afficher la lettre H lorsque les bornes A et B sont toutes les deux connectées à la borne H. Ces lettres ont toutes une signification logique.

A et B sont les entrées logiques. H est un haut logique et L est un bas logique. Le tableau de vérité pour la fonction logique ET est comme suit:

|

A |

B |

SORTIE |

|

L |

L |

L |

|

L |

H |

L |

|

H |

L |

L |

|

H |

H |

H |

En d'autres mots, A et B, tous deux doivent être à haut pour que la sortie soit haute. Le symbole logique est aussi donné à côté du schéma.

Cette fonction peut aussi être donnée comme

ou comme

ou comme

, ou comme

, ou comme

Le fonctionnement du circuit est comme suit:

Le fonctionnement du circuit est comme suit:

Quand l'une ou l'autre ou les deux entrées sont à L, la faible chute de tension dans le sens conducteur d'une diode au germanium (Ge) ou l'autre empêche le transistor PNP de se mettre en marche. Avec ce transistor arrêté, il n'y a pas de polarisation à la base du NPN qui est alors aussi arrêté. Ceci laisse le tableau d'affichage noir.

Maintenant, si les deux entrées sont à H, les deux diodes sont inversement polarisées à travers la résistance de 10K et ne remplissent aucune fonction. Cette résistance de 10K fournit la polarisation à la base du PNP pour le mettre entièrement en marche. Le NPN est aussi polarisé pour marche entière à ce point par le courant passant par la résistance de 10K à son circuit de base, le PNP et la diode au silicium (Si).

Avec le NPN en marche, le courant peut passer au tableau pour allumer l'affichage à DEL, formant la lettre H. La diode au silicium aide à assurer que le PNP est arrêté à chaque fois que le courant dans le sens conducteur d'une diode ou l'autre est présent à la base. La résistance de 22K assure que toute fuite légère de courant du PNP à l'état arrêté est empêchée de mettre en marche le NPN.

Votre voltmètre VOM peut être utilisé entre C et E pour vérifier les caractéristiques de marche et d'arrêt des transistors. Parce que les deux états logiques sont H et L, les bornes d'entrée devraient toujours être connectées à l'une des bornes. Pour ce circuit en particulier, les bornes ouvertes d'entrée sont comme une entrée haute.