C-MOS D flip-flop II

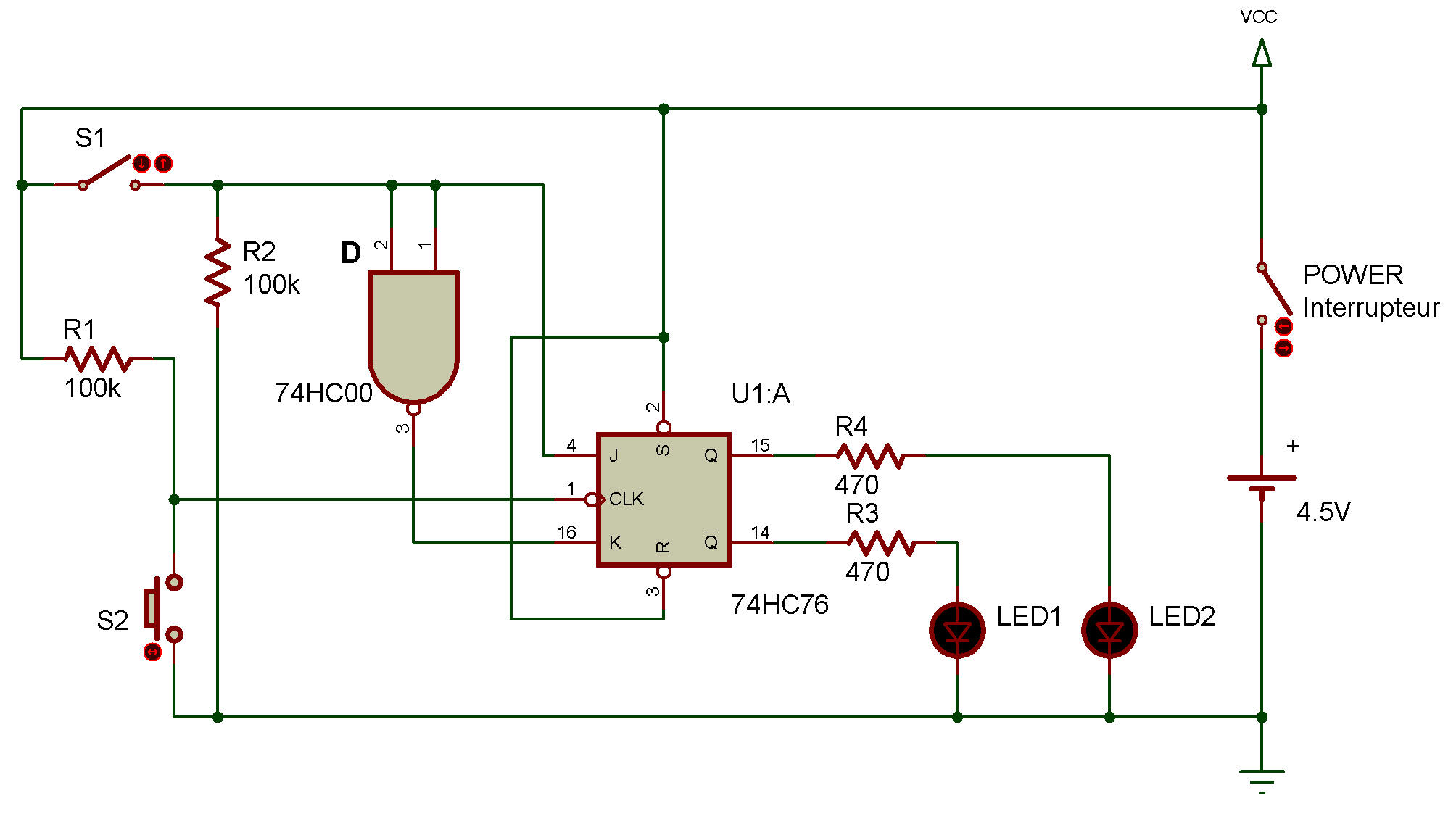

74HC00, 74HC76

We're now going to experiment with a D flip-flop circuit to find out how it works. Note it has two input terminals (D terminal and CLK terminal) and two output terminals (Q and Ǭ).

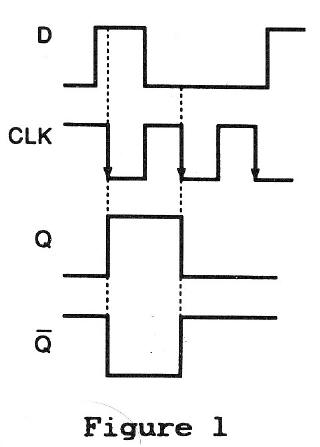

Figure 1 shows you that if you turn D terminal to 1 by pressing S1 and send a clock pulse to CLK terminal by pressing S2, the 1 and 0 levels are inverted at the output terminals Q and Ǭ, and Q becomes 1.

The output level doesn't change even if you apply 0 to D terminal, or 1 to the CLK terminal. This means that the pulse sent to the CLK terminal is "remembered" by Q. If you press S2 and send another pulse to CLK terminal, Q and Ǭ are inverted again, and this is also "remembered."

Assemble the project and turn power ON, and you'll see that either LED 1 to LED 2 lights up.

If LED 2 lights up, press S2, and this results in LED 1 lighting up and LED 2 going out. If LED 1 lights up, press S2 while pressing S1, and you'll notice LED 2 lights up and LED 1 goes out.

Now press S2 again and see what happens this time. LED 1 lights up and LED 2 goes out. Repeat this experiment while looking at Figure 1 so you can obtain a good understanding of the D flip-flop function.