Compteur de registre à décalage

Voici différents circuits intégrés de conteurs

| 4026BE | 7 segment dysplay decade counter |

| 4510BE | Presettable BCD up/down Counter |

| 4017BE | Decade counter |

| 4520 | Double compteur binaire |

| 74HC191 | Presettable Binary Up/Down Counter |

| 4029BCN | Presettable Binary/Decade Up/Down Counter |

| 14029BCP | Presettable Binary/Decade Up/Down Counter |

| 74HC193 | 4-Bit Synchronous Up/Down Counters (Dual Clock With Clear). |

| 74LS469NS | 8-Bit Binary Up-Down Counter |

| 74LS 592N | 8 Bit binary counters with intput registers |

| 74LS90 | Divide-by-12 counter decade counter and 4-Bit binary counter |

| 74LS 92N | Divide-by-12 counter decade counter |

| 74HC393 | Double compteur binaire |

| 4020 | 14-Stage Ripple Carry Binary Counters |

| 4040 | 12-Stage Ripple Carry Binary Counters |

| 74HC4060 | 14-stages binary ripple counter with oscillator |

| 4060 | 14-stages binary ripple counter with oscillator |

| 4521 | 24-stages frequency divider |

Compteur de registre à décalage

Les registres à décalage sont abordés dans les sections précédentes de cette section.

À l'aide du registre à décalage, deux types de compteurs sont conçus.

Ils sont:

• Compteur en anneau

• Comptoir Johnson

Les deux compteurs ci-dessus sont essentiellement des registres à décalage, mais comme ils génèrent des séquences d'états particulières.

Discutons des deux compteurs un par un.

Compteur en anneau (Ring Counter)

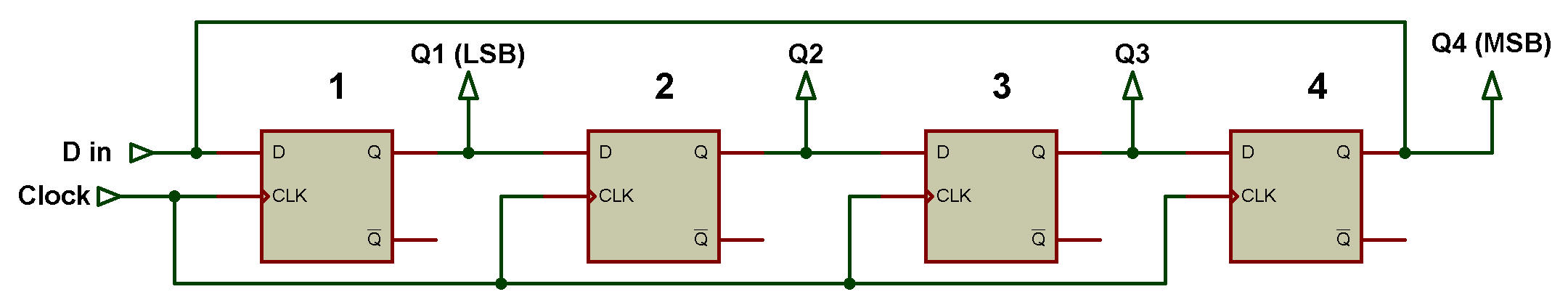

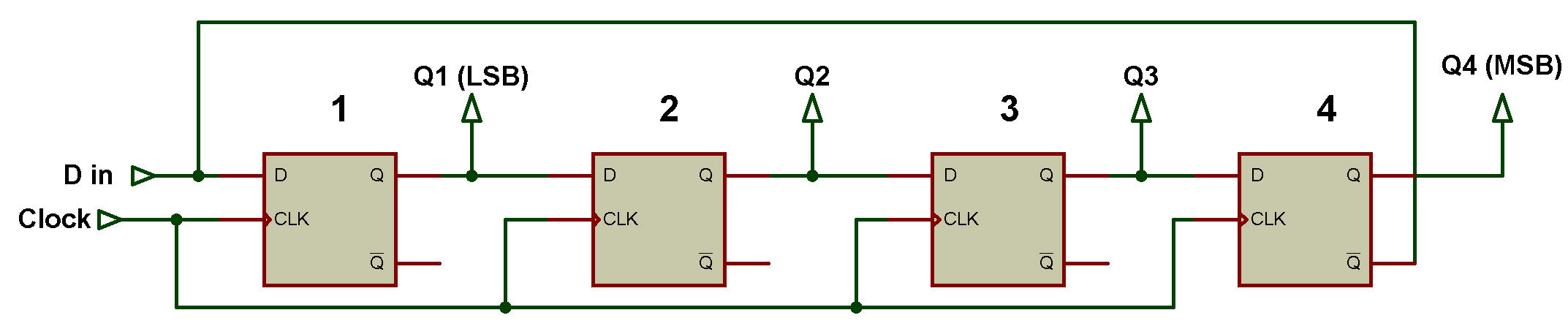

Un compteur en anneau est conçu à l'aide de registres à décalage.

La figure ci-dessous montre un compteur en anneau de 4 bits déclenché par un front positif conçu à l'aide d'une bascule D connectée en cascade.

Il s'agit en fait d'un registre à décalage circulant dans lequel la dernière bascule (MSB) décale sa valeur vers la première bascule (LSB).

Toutes les bascules sont cadencées simultanément.

Ici, la sortie Q4 est connectée à l'entrée 'D' de la bascule 1.

Le tableau de séquence est présenté dans le tableau ci-dessous:

Tableau de séquence du compteur d'anneaux

| C (clk) | Q1 | Q2 | Q3 | Q4 | Description |

| 0 | 1 | 0 | 0 | 0 | État initial |

| 1 | 0 | 1 | 0 | 0 | Q1=0,Q2=1 |

| 2 | 0 | 0 | 1 | 0 | Q2=0,Q3=1 |

| 3 | 0 | 0 | 0 | 1 | Q3=0Q4=0 |

| 4 | Répétitions du cycle | Le cycle se répète avec Q4 en entrée de la bascule 1 | |||

Initialement, avant qu'une impulsion d'horloge ne soit appliquée, la bascule 1 est défini et au repos, tous les bascules 2, 3 et 4 sont réinitialisés.

Cela signifie Q1=1 et Q2=Q3=Q4=0.

Après la première impulsion d'horloge sur front positif, Q1 passe à Q2 et donc Q1 = 0 et Q2 = 1.

Q, devient 0 car Q4 passe à Q1 et Q4=0. Donc Q1=0.

Après la 2ème impulsion d'horloge sur front positif, Q2 passe à Q3, donc Q2=0, Q3=1.

Après la troisième impulsion d'horloge sur front positif, Q3 passe à Q4. Ainsi Q3=0, Q4=1.

Ainsi, nous avons vu une seule sortie est ÉLEVÉE à la fois.

Après le 4ème front positif, l'impulsion d'horloge Q4 est décalée vers Q1.

Ainsi, Q1 = 1 et la séquence commence à se répéter.

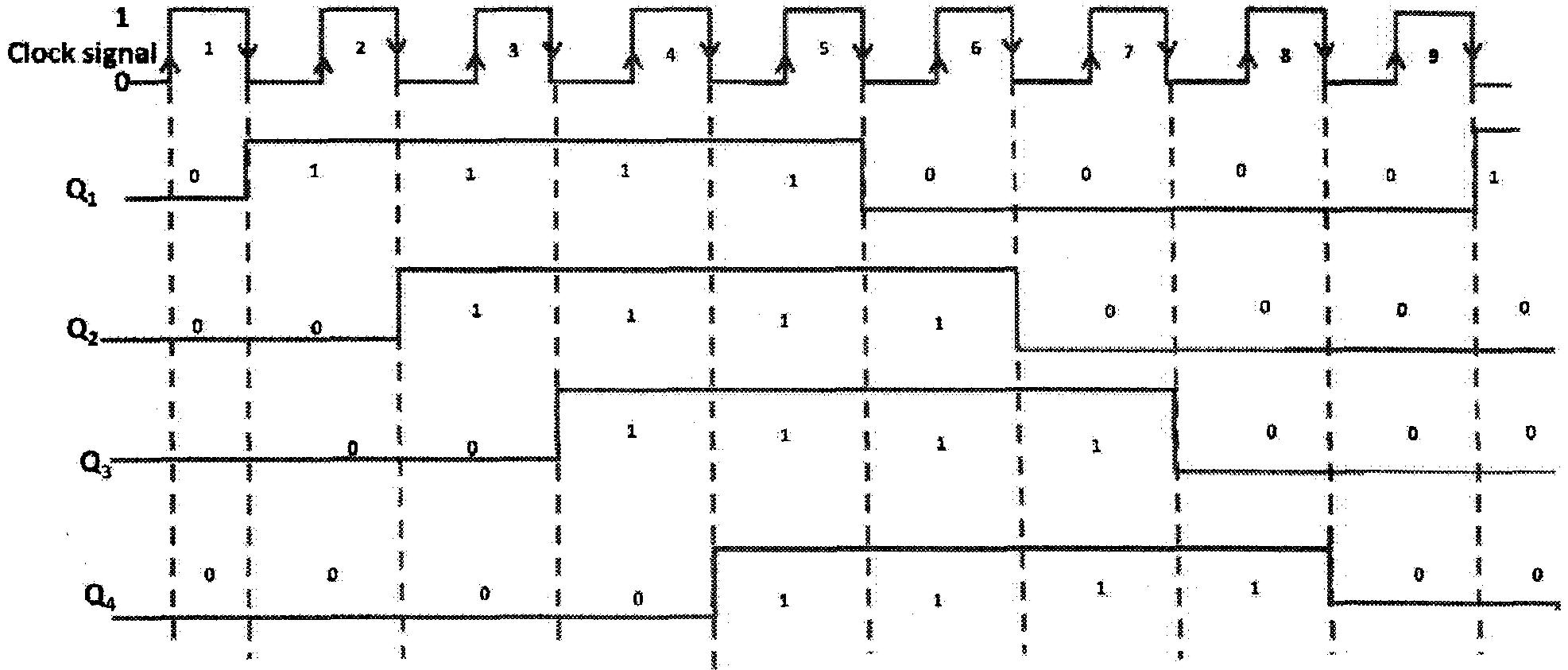

Le chronogramme est présenté à la figure ci-dessous:

Avec quatre bascules maximum 24 = 16 états sont possibles, mais seuls quatre états sont utilisés, les 12 autres états ne sont pas utilisés. L'inconvénient est que 12 États sont gaspillés (inutilisés).

L'avantage est que les compteurs en anneau sont auto-décodés. Ils sont utilisés pour coder la sortie du clavier et dans de nombreuses autres applications.

Compteur Johnson (compteur à anneaux torsadés)

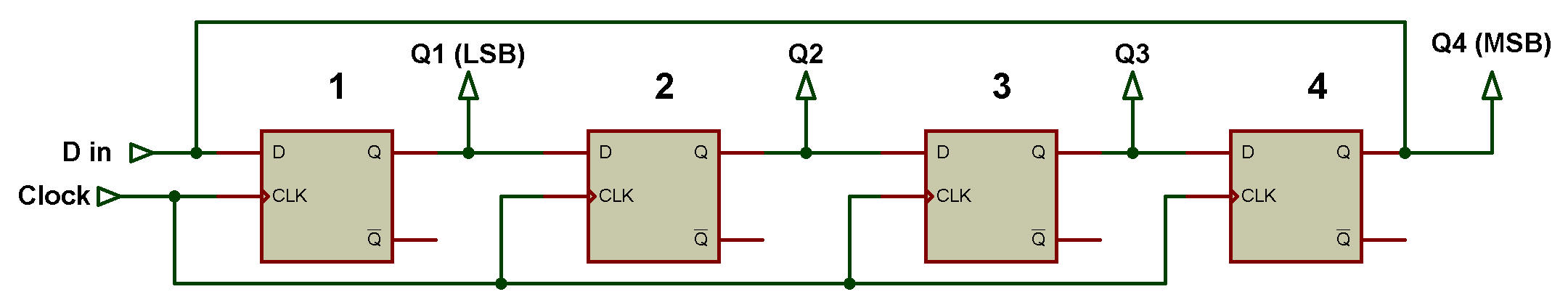

Le compteur Johnson est conçu à l'aide du registre à décalage SISO.

Il est similaire au compteur en anneau sauf qu'au lieu de la sortie originale, la sortie inversée de la dernière bascule est connectée à l'entrée D de la première bascule.

On l'appelle également compteur à anneau torsadé ou parfois compteur à queue commutée.

La figure ci-dessous montre un compteur Johnson déclenché par un front négatif de 4 bits à l'aide d'une bascule D.

Ici, la sortie Q4' de la bascule 4 est connectée à l'entrée D de la bascule 1.

Le tableau de séquence est présenté dans le tableau ci-dessous:

Tableau de séquence du compteur Johnson

| C (clk) | Q1 | Q2 | Q3 | Q4 | Q4' | Description |

| 0 | 0 | 0 | 0 | 0 | 1 | État initial |

| 1 | 1 | 0 | 0 | 0 | 1 | Q1=1 |

| 2 | 1 | 1 | 0 | 0 | 1 | Q1=Q2=1 |

| 3 | 1 | 1 | 1 | 0 | 1 | Q1=Q2=Q3=1 |

| 4 | 1 | 1 | 1 | 1 | 0 | Q1=Q2=Q3=Q4=1 |

| 5 | 0 | 1 | 1 | 1 | 0 | Q1=0 comme Q4 |

| 6 | 0 | 0 | 1 | 1 | 0 | Q1=Q2=0 |

| 7 | 0 | 0 | 0 | 1 | 0 | Q1=Q2=Q3=0 |

| 8 | 0 | 0 | 0 | 0 | 1 | Q1=Q2=Q3=Q4=0 |

| 9 | 1 | 0 | 0 | 0 | 1 | Retour à l'état initial |

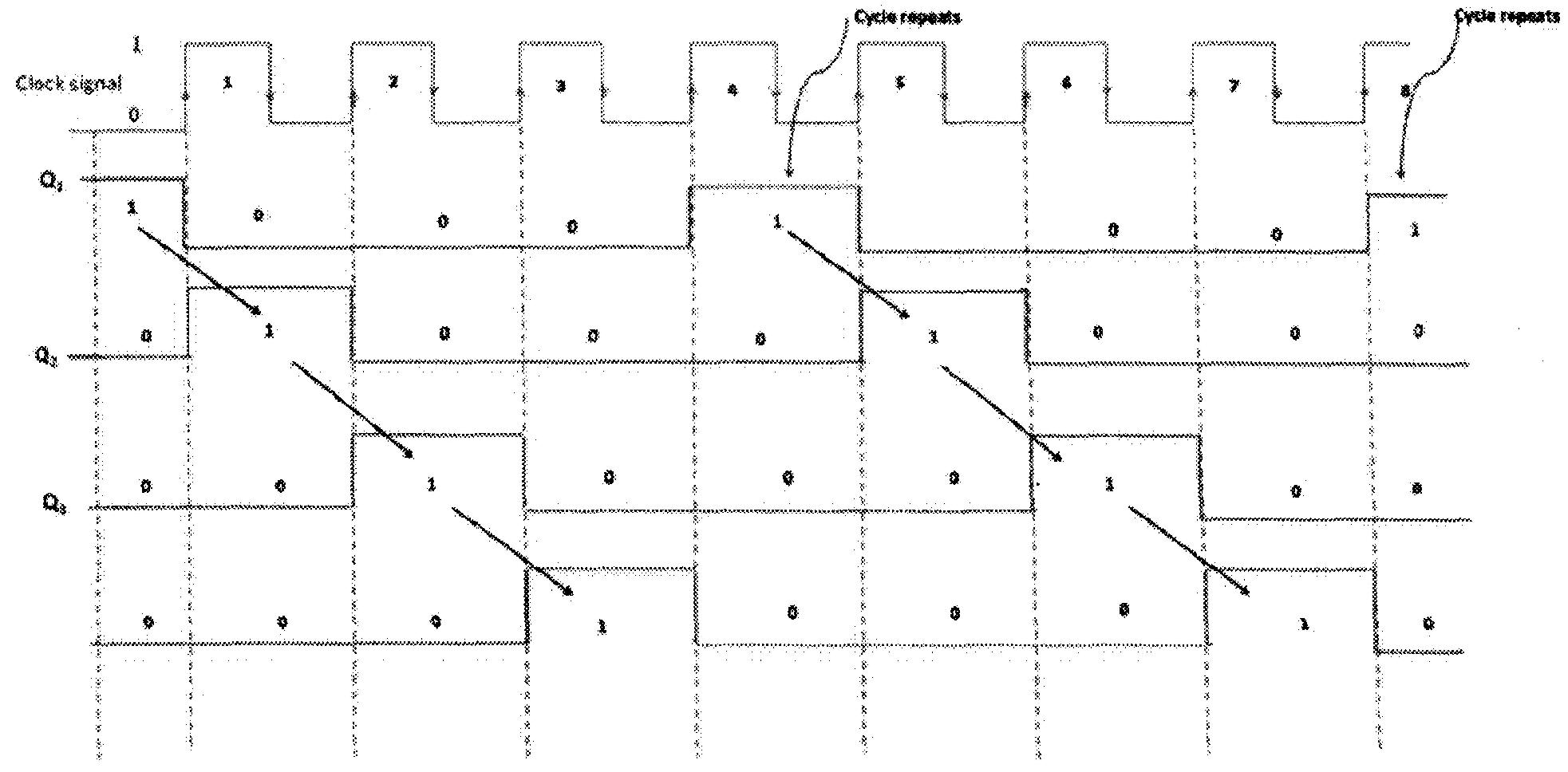

Le chronogramme du compteur Johnson 4 bits est illustré dans la figure ci-dessous: