JK et T Flips-Flops

Voir aussi Bascule (Multivibrateur)

JK JK Flip-Flop déclenchée par front positif

Dans SR JK Flip-Flop, un état invalide apparaît lorsque S = R = 1 car les deux sorties Q et Q' deviennent identiques et cela n'est pas possible car Q' est un complément de Q. Pour éviter cette condition, SR JK Flip-Flop est convertie en JK Flip-Flop.

Ici, J correspond à l'entrée S (SET) de la bascule SR et K correspond à l'entrée R (RESET).

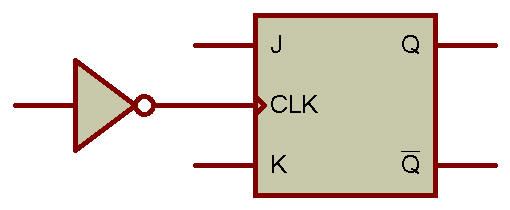

La figure ci-dessous montre le symbole logique de la bascule JK déclenchée par un front positif.

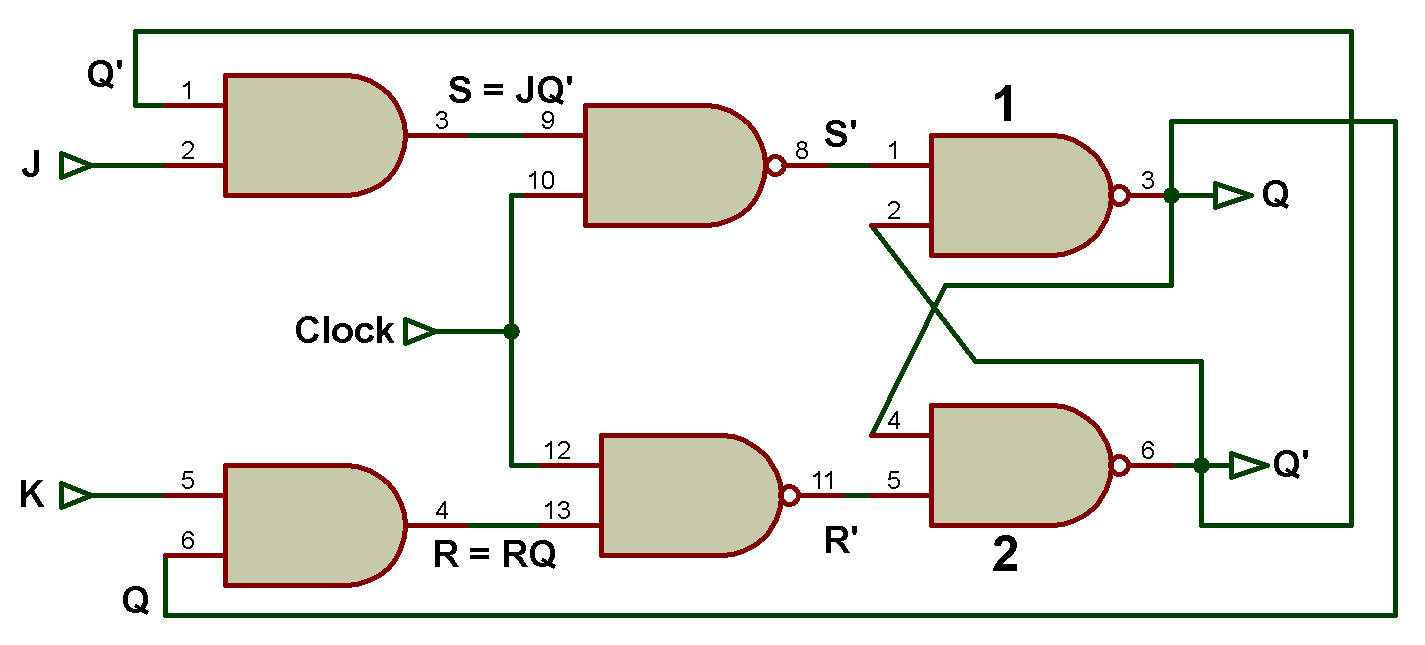

JK Flip-Flop utilisant la SR Flip-Flop et 2 portes AND supplémentaires

Le tableau ci-dessous montre la table de vérité et la figure ci-dessous montre un JK JK Flip-Flop utilisant SR Flip-Flop et 2 portes AND supplémentaires.

| Précédent | Entrées | Sorties | |||

| Q | J | K | Q | Q' | Description |

| 0 | 0 | 0 | Q(0) | Q' | La sortie ne change pas |

| 1 | 0 | 0 | Q(1) | Q' | La sortie ne change pas |

| 0 | 0 | 1 | 0 | 1 | RESET |

| 1 | 0 | 1 | 0 | 1 | RESET |

| 0 | 1 | 0 | 1 | 0 | SET |

| 1 | 1 | 0 | 1 | 0 | SET |

| 0 | 1 | 1 | Q'(1) | Q(0) | Basculements de sortie |

| 1 | 1 | 1 | Q'(0) | Q(1) | Basculements de sortie |

Différents cas de table de vérité du tableau selon les circuits de la figure ci-haut sont discutés ci-dessous.

Cas 1 : J=0, K=0

Lorsque J=K=0, alors il n’y a aucun changement dans la sortie. Cela signifie que l'état précédent de Q et Q' est maintenu.

Supposons que Q=1 et Q'=0 avant que J=K=0 ne soit appliqué en entrée, donc lorsque J=K=0 est appliqué en entrée, alors Q reste également 1 et Q' reste 0.

En effet, le circuit de la bascule JK a 2 portes ET suivies par un circuit de bascule SR (voir la figure).

Donc, S = JQ' et R = KQ

D'où S=JQ'=00=0 et R=KQ=01=0.

Avec S = 0 et R = 0 dans la bascule JK, l'état précédent Q et Q' est maintenu.

Soit maintenant Q=0 et Q'=1, puis S=01=0 et R=KQ=00=0.

Avec S = 0 et R = 0 dans la bascule JK, l'état précédent Q et Q' est maintenu.

Cas 2 : J=0, K=1 S=JQ' et R=KQ

Soient Q=0 et Q'=1 précédents, alors S=01=0 et R=KQ =10=0.

Avec S = 0 et R = 0 dans la bascule JK, l'état précédent Q et Q' est maintenu.

Soit maintenant Q=1 et Q'=0, puis S=00=0 et R=KQ=11=1.

Avec S=0 et R=1, la sortie Q devient 0 et Q' devient 1 (état RESET).

Cas 3 : J=1, K=0 S=JQ' et R=KQ

Soit Q =0 précédent et Q'=1, alors S=11=1 et R=KQ =00=0.

Avec S = 1 et R = 0 dans la sortie de la bascule JK, Q devient 1 et Q' devient 0 (état SET).

Soit maintenant Q=1 et Q'=0, alors S=10=0 et R=KQ =01=0.

Avec S = 0 et R = 0 dans la bascule JK, l'état précédent Q et Q' est maintenu.

Cas 4 : J=1, K=1 S=JQ' et R=KQ

Soient Q=0 et Q'=1 précédents, alors S=11=1 et R=KQ =10=0.

Avec S = 1 et R = 0 dans la sortie de la bascule JK, Q devient 1 et Q' devient 0 (état SET).

Soit maintenant Q=1 et Q'=0, puis S=10=0 et R=KQ =11=1.

Avec S=0 et R=1, la sortie Q devient 0 et Q' devient 1 (état RESET).

Ainsi, lorsque J = 1, K = 1, la sortie bascule. Cela signifie que Q devient Q' et Q' devient Q.

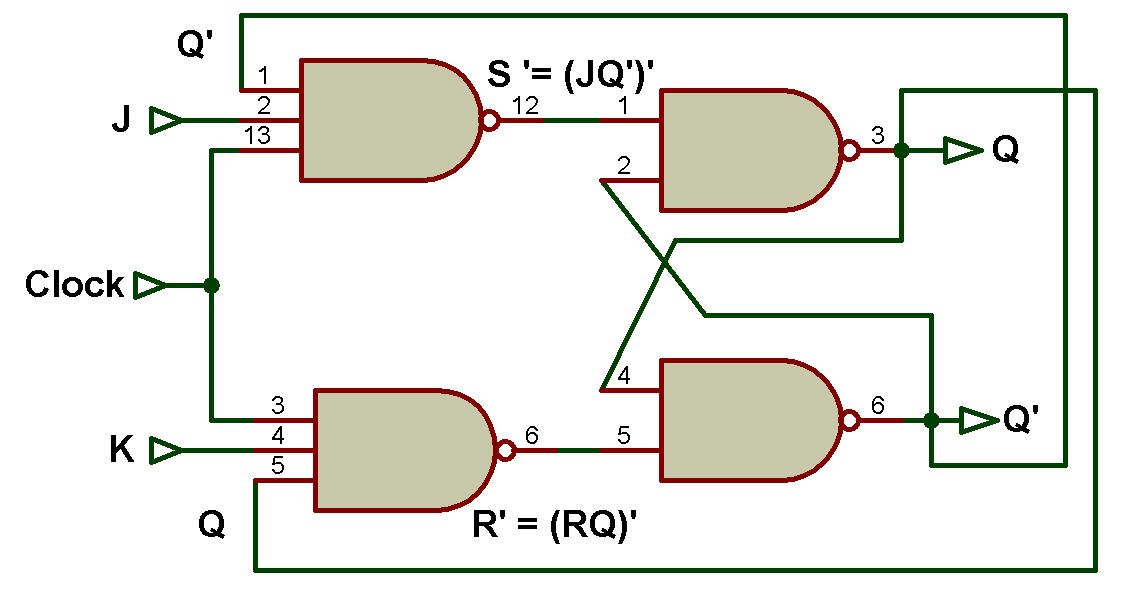

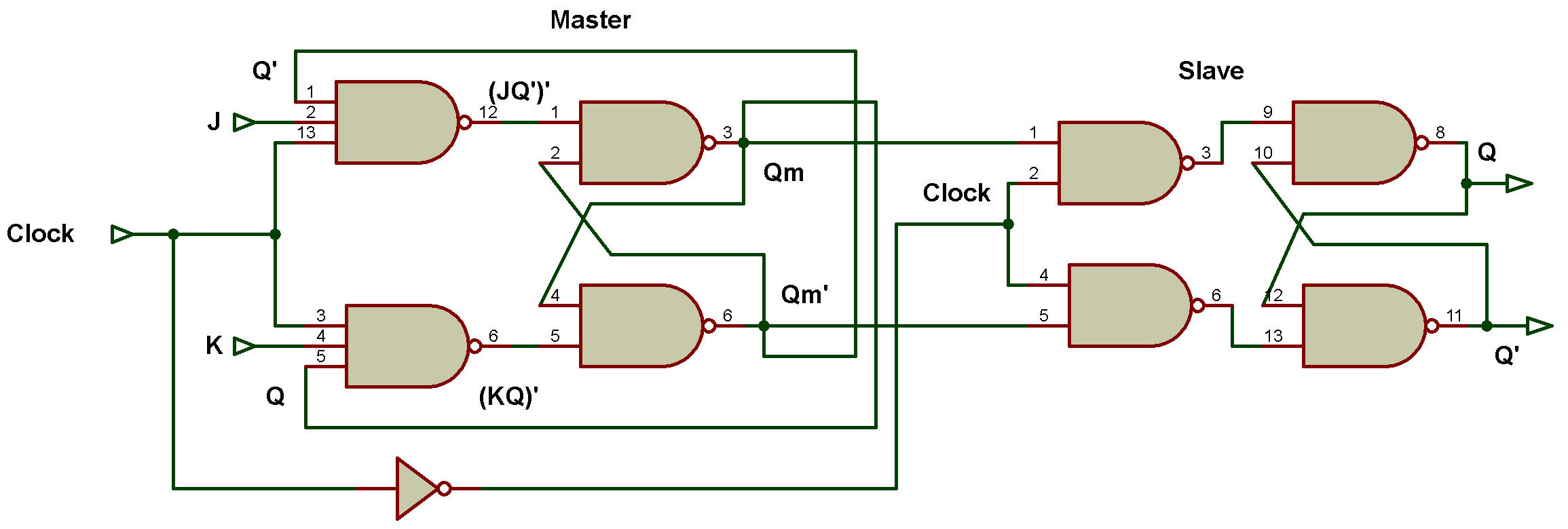

JK Flip-Flop de la figure ci-haut peut également être conçue en utilisant des portes NAND comme le montre la figure ci-dessous.

La fonctionnalité et la table de vérité restent les mêmes.

Prenons n'importe quel cas pour comprendre le circuit de la figure.

Cas : J=0 et K=1

S'=(JQ')' et R'=(KQ)'

Soient Q=0 et Q'=1 précédents, alors S'=01=0 et R'=10=0.

Avec S = R = 0 dans la sortie de bascule JK, Q et Q' restent inchangés (l'état précédent est maintenu).

Soit maintenant Q=1 et Q'=0, puis S'=00=0 et R'=11=1.

Avec S=0 et R=1 dans la sortie de la bascule JK Q =0 et Q0=1 (état RESET).

JK Flip-Flop déclenchée par un front négatif

La fonctionnalité de JK Flip-Flop déclenchée par un front négatif est la même que celle de JK Flip-Flop déclenchée par un front positif, sauf que le Flip-Flop déclenchée par le front négatif modifie la sortie (réagit à l'entrée) uniquement sur le front négatif (descendant) de l'impulsion d'horloge.

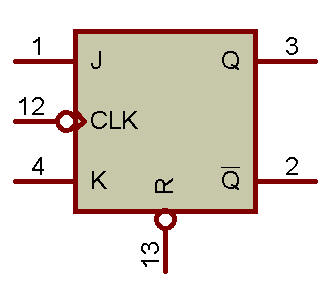

La figure ci-dessous montre les symboles logiques du front négatif déclenché par JK Flip-Flop.

La porte NOT à l'entrée de l'impulsion d'horloge montre que le Flip-Flop est déclenchée par le front négatif.

La figure ci-dessous montre les symboles logiques du JK Flip-Flop déclenchée par le front négatif. La bulle (cercle) à l'entrée de l'impulsion d'horloge (CLK) montre que la bascule est déclenchée par le front négatif. Ce Flip-Flop a aussi un RESET (R).

Master-Slave JK Flip-Flop (Maître-Esclave)

Le Flip-Flop JK maître-esclave est illustrée à la figure ci-dessous:

Il se compose d'un maître et d'un esclave.

La première est un JK Flip-Flop cadencée qui fait office de maître et la seconde est un SR Flip-Flop cadencée qui fait office d'esclave. Le signal d'horloge est connecté directement à la bascule maître et est connecté via l'inverseur (NOT) à la bascule esclave.

Lorsque l'impulsion d'horloge est élevée, la bascule maître est activée et la bascule esclave est désactivée.

La sortie de la bascule principale change en fonction de l'entrée sur le front positif (front montant) de l'horloge et la sortie reste inchangée sur le front négatif (front descendant) de l'impulsion d'horloge.

La sortie du maître change à nouveau lorsque l'impulsion d'horloge passe à nouveau de bas en haut, c'est-à-dire sur le front positif (front montant) de l'impulsion d'horloge.

De même, l'esclave est activé sur le front négatif (descendant) de l'impulsion d'horloge. La sortie du maître QM agit comme une entrée pour l'esclave et l'esclave ne répond à l'entrée qu'au front négatif de l'impulsion d'horloge.

La sortie reste inchangée en cas de front positif (front montant). La sortie de l'esclave change à nouveau lorsque l'impulsion d'horloge passe à nouveau de haut en bas, c'est-à-dire sur le front négatif (front descendant) de l'impulsion d'horloge.

Notez que :

La porte NAND 3 et la porte NAND 4 à couplage croisé avec la sortie Qm alimentée en entrée de la porte NAND 4 et la sortie Qm' alimentée en entrée de la porte NAND 3.

Ce circuit forme un SR Latch en utilisant la porte NAND. La table de vérité pour SR Latch utilisant la porte NAND est présentée dans le tableau ci-dessous:

Table de vérité pour le SR Latch utilisant la porte NAND

| Entrées | Sorties | |||

| S | R | Q | Q' | Description |

| 0 | 0 | - | - | Invalide |

| 0 | 1 | 1 | 0 | SET |

| 1 | 0 | 0 | 1 | RESET |

| 1 | 1 | Q | Q' | La sortie ne change pas |

Cas 1 (a) :

J=0 et K=1 avec Q=1 précédent et Q'=0 précédent sur le front positif de l'impulsion d'horloge (le maître est activé)

Maintenant, la sortie de la porte NAND 1 = (JQ')' = (00)' =1

La sortie de la porte NAND 2 = (KQ)' - (11)' = 0

L'entrée 'S' correspond à l'entrée A (1) et 'R' correspond à l'entrée B (5) de la figure

Entrée de la porte NAND 3 = (AQm') = (1Qm')

Entrée de la porte NAND 4 = (BQm) = (0Qm)

En référence à la figure, sortie finale Q=1 et Q'=0 (sortie non modifiée)

Cas 1 (b) :

J=0 et K=1 avec Q=1 précédent et Q'=0 précédent sur le front négatif de l'impulsion d'horloge (l'esclave est activé)

Maintenant, S=Qm=0 Donc, la sortie de la porte NAND 5=(S)'=(A)=1

R = Qm' = 1 Donc, sortie de la porte NAND 6 = (R)' = (B) = 0

Entrée de la porte NAND 7=(S'Q')=(AQ')=1Q'

Entrée de la porte NAND 8=(R'Q)=(BQ)=0Q

En référence à la figure, la sortie finale Q=0 et Q'=1

Cas 1 (c) :

J=0 et K=1 avec Q=0 précédent et Q'=1 précédent sur le front positif de l'impulsion d'horloge (le maître est activé)

Maintenant, la sortie de la porte NAND 1 =(JQ')'=(01)'=1

La sortie de la porte NAND 2=(KQ)'=(10)'=1

L'entrée 'S' correspond à l'entrée A et 'R' correspond à l'entrée B de la Figure

Entrée de la porte NAND 3=(AQM')=0Qm')

Entrée de la porte NAND 4=(BQm)=(1Qm)

En référence à la figure, la sortie finale Q = 0 et Q' = 1 (sortie non modifiée)

Cas 1 (d) :

J=0 et K=1 avec Q=0 précédent et Q'=1 précédent sur le front négatif de l'impulsion d'horloge (l'esclave est activé)

Maintenant, S=Qm=0 Donc, sortie de la porte NAND 5=(S)'=(A)=1

R = Qm'= 1 Donc, sortie de la porte NAND 6=(R)'=(B)=0

Entrée de la porte NAND 7=(S'Q')=(AQ')=1Q'

Entrée de la porte NAND 8 = (R'Q)=(BQ)=0Q

En référence à la figure, la sortie finale Q=0 et Q'=1.

De même, les conditions 2(a) à 2(d), 3(a) à 3(d) et 4(a) à 4(d) peuvent être formées.

Cas 2 (a) : J=1 et K=0 avec Q=0 précédent et Q'=1 précédent sur le front positif de l'impulsion d'horloge (le maître est activé)

Cas 2 (b) : J=1 et K=0 avec Q=0 précédent et Q'=1 précédent sur le front négatif de l'impulsion d'horloge (l'esclave est activé)

Cas 2 (c) : J=1 et K=0 avec Q=1précédent et Q'=0 précédent sur le front positif de l'impulsion d'horloge (le maître est activé)

Cas 2 (d) : J=1 et K=0 avec Q=1 précédent et Q'=0 précédent sur le front négatif de l'impulsion d'horloge (l'esclave est activé)

Cas 3 (a) : J=0 et K=0 avec Q=1 précédent et Q'=0 précédent sur le front positif de l'impulsion d'horloge (le maître est activé)

Cas 3 (b) : J=0 et K=0 avec Q=1 précédent et Q'=0 précédent sur le front négatif de l'impulsion d'horloge (l'esclave est activé)

Cas 3 (c) : J=0 et K=0 avec Q=0 précédent et Q'=1 précédent sur le front positif de l'impulsion d'horloge (le maître est activé)

Cas 3 (d) : J=0 et K=0 avec Q=0 précédent et Q'=1 précédent sur le front négatif de l'impulsion d'horloge (l'esclave est activé)

Cas 4 (a) : J=1 et K=1 avec Q=0 précédent et Q'=1 précédent sur le front positif de l'impulsion d'horloge (le maître est activé)

Cas 4 (b) : J=1 et K=1 avec Q=0 précédent et Q'=1 précédent au front négatif de l'impulsion d'horloge (l'esclave est activé)

Cas 4(c) : J=1 et K=1 avec Q=1 précédent et Q'=0 précédent sur le front positif de l'impulsion d'horloge (le maître est activé)

Cas 4(d) : J=1 et K=1 avec Q=1précédent et Q'=0 précédent sur le front négatif de l'impulsion d'horloge (l'esclave est activé)

Toutes ces 8 conditions de l(a) à 4(d) sont résumées dans le tableau ci-dessous:

| Clock | Précédent | Entrées | Sorties | ||||

| C | Q | J | K | Qm | Q | Q' | Cas |

| ↑ | 1 | 0 | 1 | 0 | Ne change pas | Ne change pas | Cas 1(a) |

| ↓ | 1 | 0 | 1 | Ne change pas | 0 | 1 | Cas 1(b) |

| ↑ | 0 | 0 | 1 | 0 | Ne change pas | Ne change pas | Cas 1(c) |

| ↓ | 0 | 0 | 1 | Ne change pas | 0 | 1 | Cas 1(d) |

| ↑ | 0 | 1 | 0 | 1 | Ne change pas | Ne change pas | Cas 2(a) |

| ↓ | 0 | 1 | 0 | Ne change pas | 1 | 0 | Cas 2(b) |

| ↑ | 1 | 1 | 0 | 1 | Ne change pas | Ne change pas | Cas 2(c) |

| ↓ | 1 | 1 | 0 | Ne change pas | 1 | 0 | Cas 2(d) |

| ↑ | 1 | 0 | 1 | 1 | Ne change pas | Ne change pas | Cas 3(a) |

| ↓ | 1 | 0 | 1 | Ne change pas | 1 | 0 | Cas 3(b) |

| ↑ | 0 | 0 | 1 | 0 | Ne change pas | Ne change pas | Cas 3(c) |

| ↓ | 0 | 0 | 1 | Ne change pas | 0 | 1 | Cas 3(d) |

| ↑ | 0 | 1 | 0 | 1 | Ne change pas | Ne change pas | Cas 4(a) |

| ↓ | 0 | 1 | 0 | Ne change pas | 1 | 1 | Cas 4(b) |

| ↑ | 1 | 1 | 0 | 0 | Ne change pas | Ne change pas | Cas 4(c) |

| ↓ | 1 | 1 | 0 | Ne change pas | 0 | 1 | Cas 4(d) |

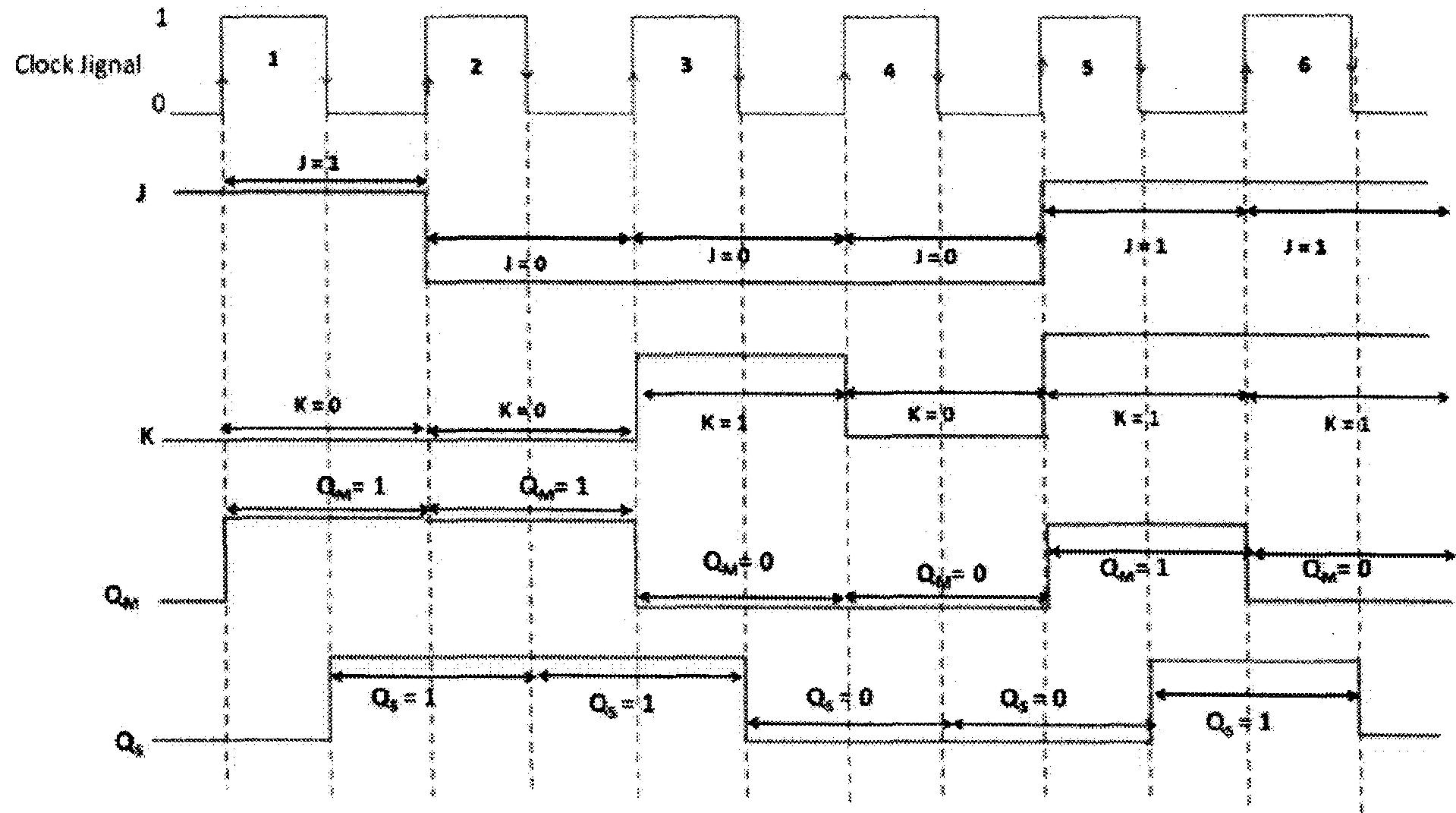

Le chronogramme (forme d'onde d'entrée/sortie) du maître-esclave de la bascule JK est illustré dans la figure ci-dessous:

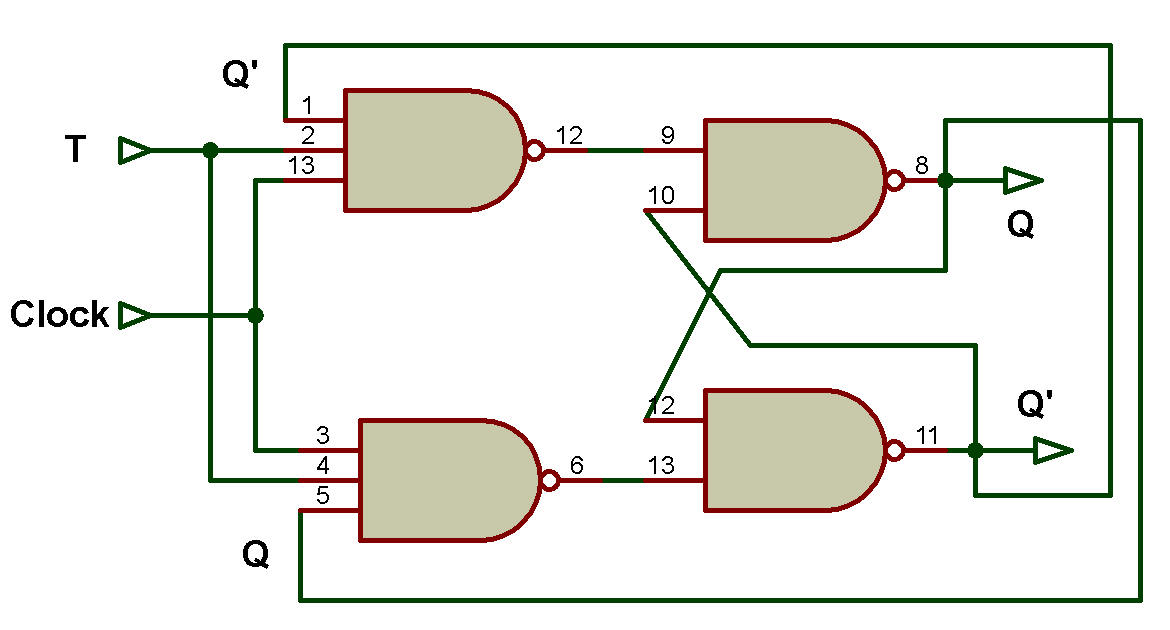

T Flip-Flop

T flip-flop est également connue sous le nom de bascule "Toggle". Le flip-flop T est obtenue à partir d'un JK flip-flop connectant ensemble les entrées J et K et lui donnant le nom 'T'

La flip-flop Toggle (T) est illustrée à la figure ci-dessous:

Le symbole logique est présenté dans la figure et la table de vérité sont présentées ci-dessous:

| Précédent | Entrées | Sorties | |

| Q | T | Q | Q' |

| 0 | 0 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

Lorsque T=0 alors J=K=0 (voir Figure). Selon la bascule JK, lorsque J=K=0, les sorties Q et Q' conservent leur état précédent.

Lorsque T=1 alors J=K=1 (voir Figure). Selon la bascule JK, lorsque J = K = 1, la sortie bascule, cela signifie que Q devient Q' et Q' devient Q.