Latch (Verrous)

Introduction :

En électronique numérique, un Latch est un dispositif bistable (ou on peut dire une sorte de multivibrateur bistable) capable de rester dans l'un ou l'autre des deux états. Ces deux états sont SET et RESET.

Les bascules sont également le dispositif bistable (multivibrateur bistable) similaire aux verrous. Les Flip-Flops ont également deux états.

Le Latch (verrou) et la bascule sont tous deux des éléments de stockage de base des circuits séquentiels et tous deux sont capables de stocker 1 bit d'informations. La différence entre le verrou et les bascules est la suivante :

• Latch est asynchrone, c'est-à-dire indépendant de l'impulsion d'horloge. La sortie change immédiatement lorsque l'entrée change, à condition que Enable soit High. Si Enable est faible, Latch conserve son état précédent même si l'entrée change.

D'un autre côté, les Flip-Flops (bascules) sont synchrones et dépendent du signal d'horloge. La bascule est déclenchée par un front positif ou négatif du signal d'horloge pour un changement de leur état de sortie.

Une bascule est déclenchée par un front positif si la sortie de la bascule change avec le changement d'entrée uniquement lorsque le signal d'horloge passe de l'état bas à l'état haut (transition d'état) et la bascule est déclenchée par un front négatif si la sortie de la bascule est déclenchée par un front positif change avec le changement d'entrée uniquement lorsque le signal d'horloge passe de l'état haut à l'état bas (transition d'état).

• Les Latch sont sensibles au niveau, ce qui signifie que la sortie change avec le changement d'entrée uniquement lorsque le verrou est haut (+5 V), ce qui signifie que le verrou est activé. Une fois éteints, ils conservent le dernier état de sortie car leur niveau est bas (+0 volts).

Les Flip-Flops, sont déclenchées par un front, ce qui signifie que la sortie change avec les changements d'entrée uniquement lorsque l'impulsion d'horloge passe de haut en bas (bord négatif déclenché) ou de bas en haut (bord positif déclenché).

SR Latch

SR Latch est l’un des types de Latch les plus simples. Il s'agit d'un verrou Set-Reset (SR).

Il peut être construit soit en utilisant deux portes NOR à couplage croisé, soit en deux portes NAND à couplage croisé. Nous discuterons également du SR Latch avec une entrée d'activation (ou de contrôle).

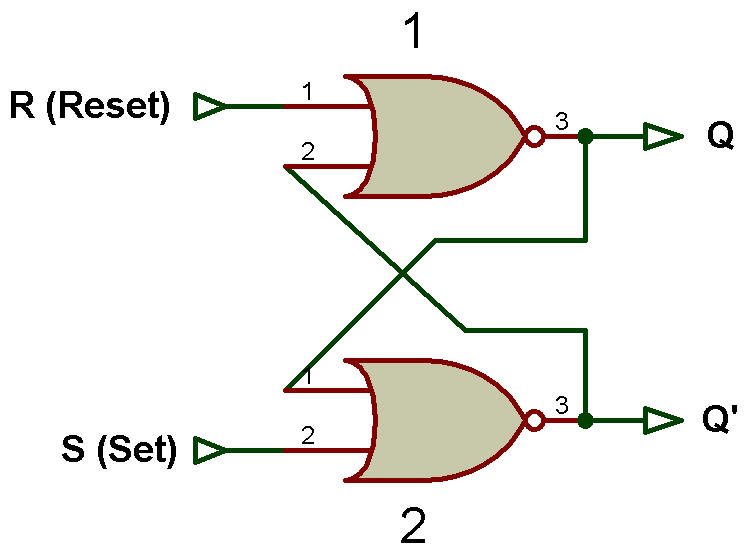

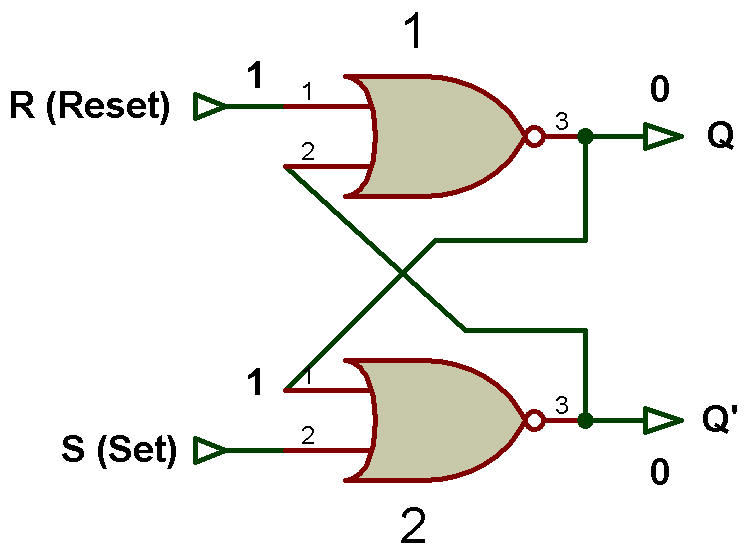

SR Latch utilisant la porte NOR

La figure ci-dessous montre le SR Latch utilisant deux portes NOR à couplage croisé. Le SR Latch utilisant la porte NOR est actif-haut. Le SR Latch signifie que le Latch effectuera l'opération souhaitée lorsqu'il est haut (1).

Comme le montre la figure, les deux portes NOR sont connectées de telle sorte que la sortie de la porte NOR 1 est connectée à l'une des entrées de la porte NON-OU 2 et la sortie de la porte NOR 2 est connectée à l'une des entrées de la porte NOR 1.

La sortie de la porte NOR 1 est Q et celle de la porte NOR 2 est Q'.

S (Set) et R (Reset) sont les entrées de la porte NOR 2 et de la porte NOR 1, respectivement.

Le tableau des fonctions du SR Latch utilisant deux portes NOR à couplage croisé est présenté dans le tableau ci-dessous:

Tableau fonctionnel du SR Latch utilisant la porte NOR

| Entrées | Sorties | |||

| S | R | Q | Q' | Description |

| 1 | 0 | 1 | 0 | SET |

| 0 | 0 | 1 | 0 | La sortie ne change pas (la sortie précédente est conservée) |

| 0 | 1 | 0 | 1 | RESET |

| 0 | 0 | 0 | 1 | La sortie ne change pas (la sortie précédente est conservée) |

| 1 | 1 | 0 | 0 | État INTERDIT (INVALIDE) |

Discutons du tableau fonctionnel pour différentes combinaisons de valeurs de S et R.

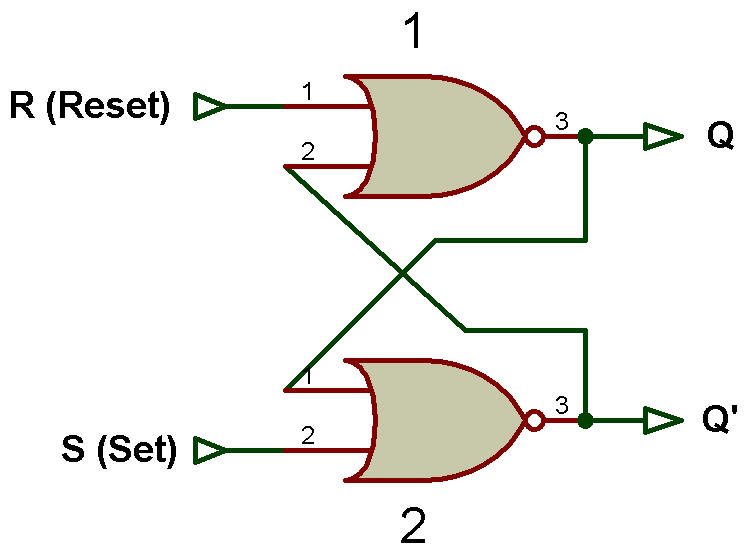

Cas 1: S = 1 et R = 0

Comme le montre la figure,

l'entrée S de la porte NOR 2 est « 1 », donc la sortie Q = 0, ce qui fait que

l'entrée de la porte NOR 1 est 0,0. La sortie Q de la porte NON-OU 1 devient

'1'. Ainsi Q = 1 et Q' = 0.

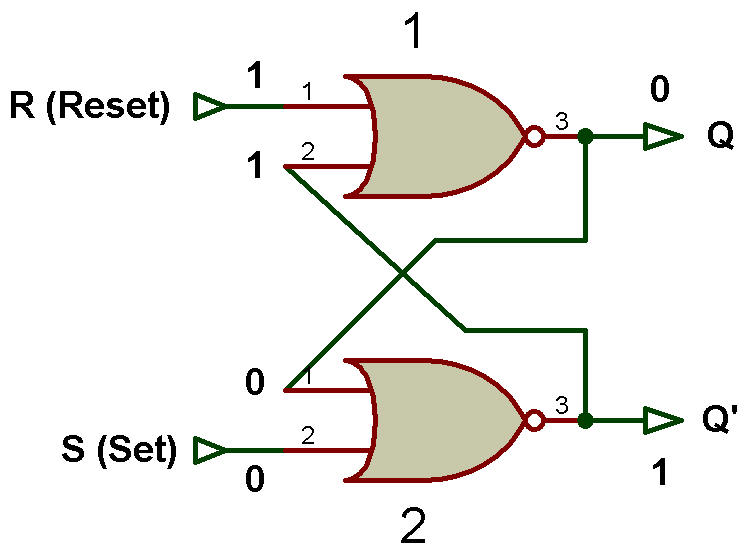

Cas 2: S = 0 et R = 1

Comme le montre la figure, l'entrée R de la porte NOR 1 est égale à « 1 », donc la sortie Q devient « 0 », ce qui rend les entrées de la porte NOR 2 égales à 0,0. Ainsi, la sortie Q' de La porte NOR 2 devient « 1 ».

Par conséquent, lorsque S = 0 et R =1 , la sortie Q = 0 et Q' = 1 car l'entrée R (Reset) est au niveau haut actif (1).

Cas 3 : S = 0 et R = 0

Lorsque les deux entrées S et R sont égales à « 0 », alors dans cette condition, aucun changement n'est produit et la valeur précédente de Q et Q' est maintenue.

Supposons que Q = 1 et Q = 0. Désormais, lorsque les entrées S = 0 et R = 0 sont appliquées aux portes NOR 2 et 1, le scénario est illustré à la figure.

L'entrée de la porte NOR 1 est 0,0 donc la sortie Q = 1. L'entrée de la porte NOR 2 est 1,0 donc la sortie Q' = 0. Cela montre que lorsque S = R = 0, alors les sorties Q et Q' ne changent pas et conservent leurs valeurs précédentes.

Cas 4 : S = 1 et R = 1

Comme le montre la figure, lorsque S = R = 1, l'entrée des deux portes NOR sont à 1 logique, ce qui fait que les sorties Q et Q' deviennent « 0 ».

Il s'agit d'une condition invalide car Q et Q' ne peuvent pas être nuls en même temps car Q' est un complément de Q et donc si Q=0 alors Q' doit être 1. Ainsi, lorsque S=R=1, c'est un état invalide ou illégal.

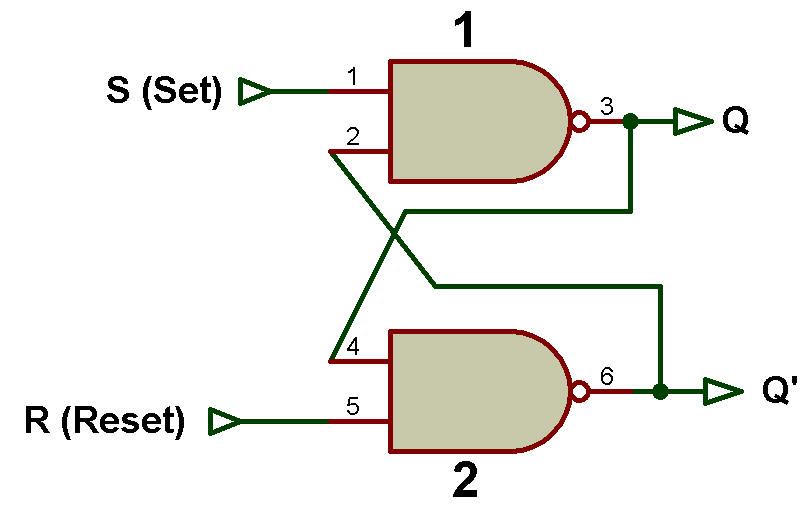

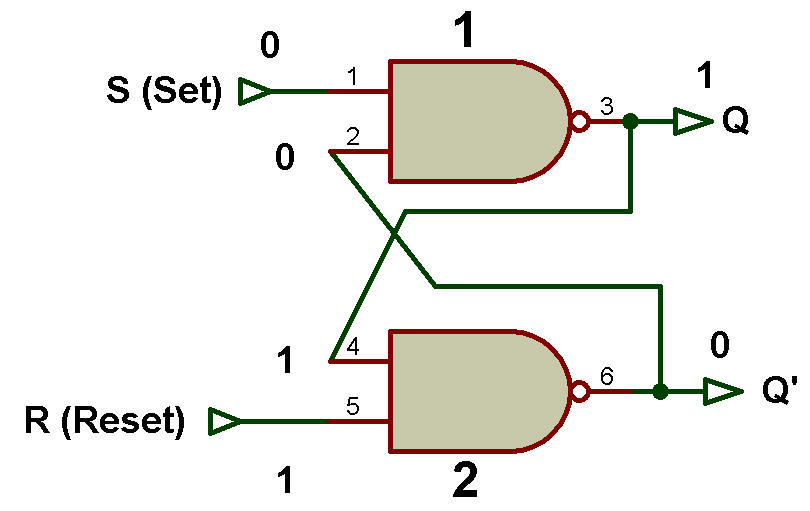

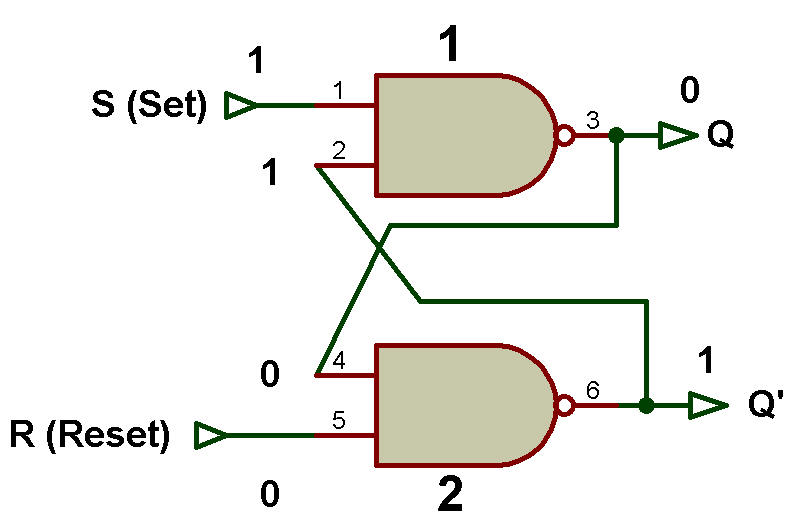

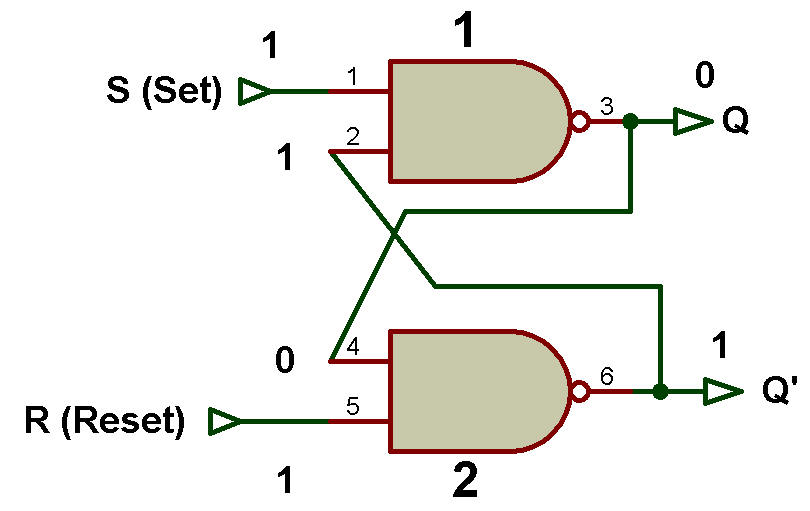

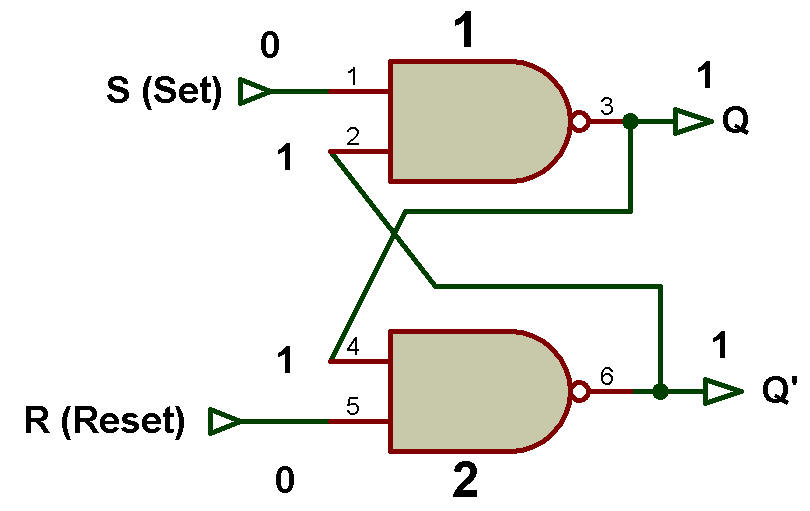

SR Latch utilisant la porte NAND

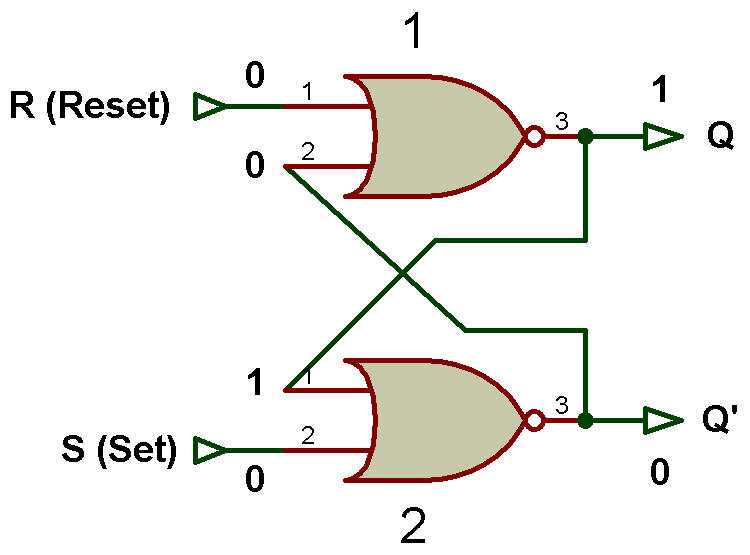

La figure ci-dessous montre SR Latch utilisant deux portes NAND à couplage croisé. Le SR Latch utilisant la porte NAND est un SR Latch actif-bas, ce qui signifie qu'il effectuera l'opération souhaitée lorsqu'il est BAS (0).

Comme le montre la figure, les deux portes NAND sont connectées de telle sorte que la sortie de la porte NAND 1 est connectée à l'une des entrées de la porte NAND 2 et la sortie de la porte NAND 2 est connectée à l'une des entrées de la porte NAND 1.

La sortie du NAND 1 est Q et celle de la porte NAND 2 est Q'.

Le tableau fonctionnel du SR Latch de la porte NAND est présenté dans le tableau ci-dessous:

Tableau fonctionnel du SR Latch utilisant la porte NAND

| Entrées | Sorties | |||

| S | R | Q | Q' | Description |

| 0 | 1 | 1 | 0 | SET |

| 1 | 1 | 1 | 0 | La sortie ne change pas (la sortie précédente est conservée) |

| 1 | 0 | 0 | 1 | RESET |

| 1 | 1 | 0 | 1 | La sortie ne change pas (la sortie précédente est conservée) |

| 0 | 0 | 1 | 1 | État INTERDIT (INVALIDE) |

Le SR Latch utilisant la porte NAND est actif-bas. Le SR Latch signifie qu'il effectue l'opération souhaitée lorsque le signal est faible (0).

Cas 1 : S = 0 et R = 1, le SR Latch est défini car l'entrée « S » reçoit une entrée active basse (0) et donc une sortie Q = 1 comme indiqué sur la figure ci-dessous:

Cas 2 : S = l et R = 0, le SR Latch est réinitialisé car l'entrée « R » est fournie avec une entrée active basse (0), donc la sortie Q = 0. Ceci est illustré à la figure ci-dessous:

Cas 3 : S et R au niveau logique 1 signifie S=R=1, il n'y a aucun changement dans la sortie et la sortie conserve son état précédent. Ceci est illustré à la figure ci-dessous:

Cas 4 : S = R = 0, c'est un état invalide et Q = Q' = 1. Ceci est illustré dans la figure ci-dessous:

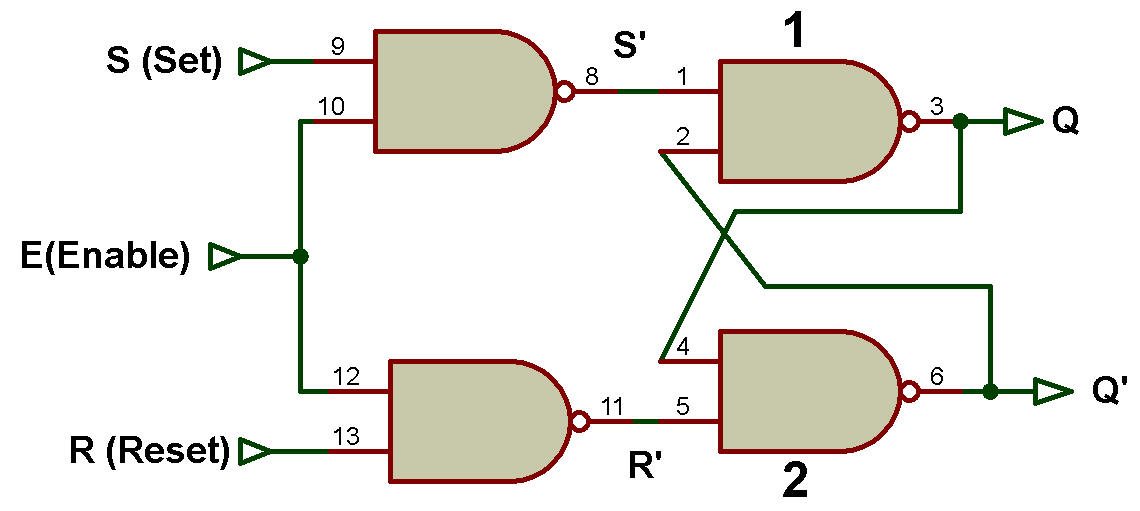

SR Latch avec entrée de contrôle ou entrée d'activation

Dans SR Latch avec Enable ou entrée de contrôle, il y a une entrée supplémentaire E (Enable). Le SR Latch avec entrée Enable est également connu sous le nom de SR Latch fermé. L'entrée Enable (E) permet d'activer ou de désactiver SR Latch.

Le SR Latch avec activation (E) utilisant des portes NAND est illustré à la figure ci-dessous:

Le tableau fonctionnel du SR Latch utilisant la porte NAND est présenté dans le tableau ci-dessous:

| Entrées | Sorties | ||||

| E | S | R | Q | Q' | Description |

| 1 | 0 | 0 | Q | Q' | La sortie ne change pas |

| 1 | 0 | 1 | 0 | 1 | RESET |

| 1 | 0 | 0 | 0 | 1 | La sortie ne change pas (la sortie précédente est conservée) |

| 1 | 1 | 0 | 1 | 0 | SET |

| 1 | 0 | 0 | 1 | 0 | La sortie ne change pas (la sortie précédente est conservée) |

| 1 | 1 | 1 | 0 | 0 | État INTERDIT (INVALIDE) |

| 0 | x | x | Q | Q' | La sortie ne change pas |

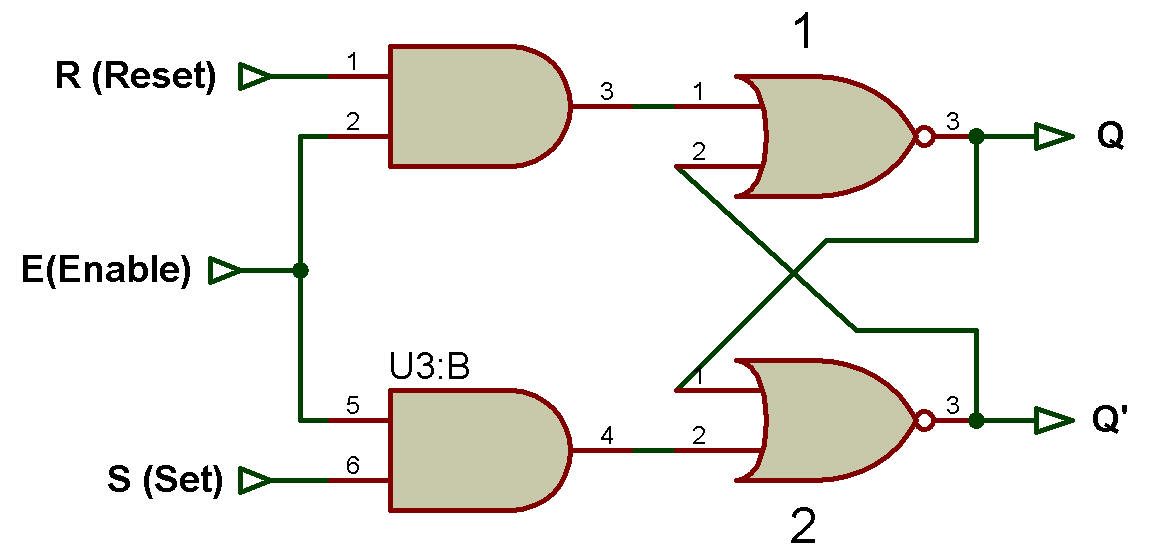

Le SR Latch avec Enable (E) utilisant des portes NOR est illustré à la figure 3.5(b).

Le tableau fonctionnel du SR Latch utilisant la porte NOR est présenté dans le tableau qui est le même que le tableau ci-haut.

D Latch

L'un des problèmes avec SR Latch est que lorsque les entrées S et R sont à « 1 » en même temps, cet état n'est pas valide car les sorties Q et Q' deviennent « 0 ». Ceci n'est pas possible (contradictoire) car Q est le complément de Q'.

Ce problème est éliminé en utilisant 'D' (D pour données) Latch. Le D Latch est également connu sous le nom de Latch transparent.

Le D Latch utilisant la porte NAND, la porte NOR et le D Latch avec entrée d'activation ou de contrôle (ou D Latch à porte) seront abordés dans les sections suivantes.

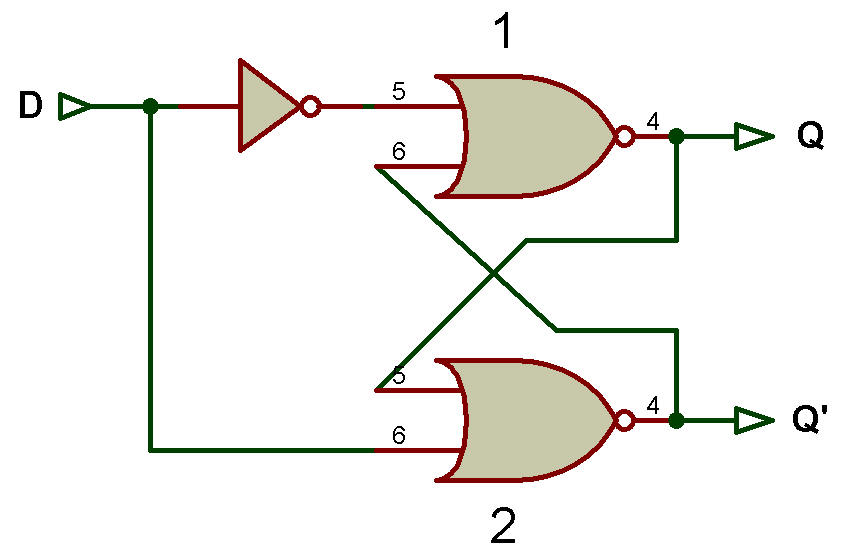

D Latch utilisant la porte NAND

Le D Latch utilisant la porte NAND est illustré à la figure ci-dessous:

Comme le montre la figure 3.6(a), le Latch n'a qu'une seule entrée D (Données).

L'entrée 'D' est directement connectée à l'entrée 'S' et le complément de l'entrée 'D' est connecté à l'entrée 'R'.

Si D = 1, la sortie Q devient 1. Si D = 0, la sortie Q devient 0.

Ceci est indiqué dans le tableau ci-dessous:

| D | Q | Q' |

| 1 | 1 | 0 |

| 0 | 0 | 1 |

D Latch utilisant la porte NOR

Le D Latch utilisant la porte NOR est illustré à la figure ci-dessous:

La table de vérité est affichée ci-dessous:

| D | Q | Q' |

| 1 | 1 | 0 |

| 0 | 0 | 1 |

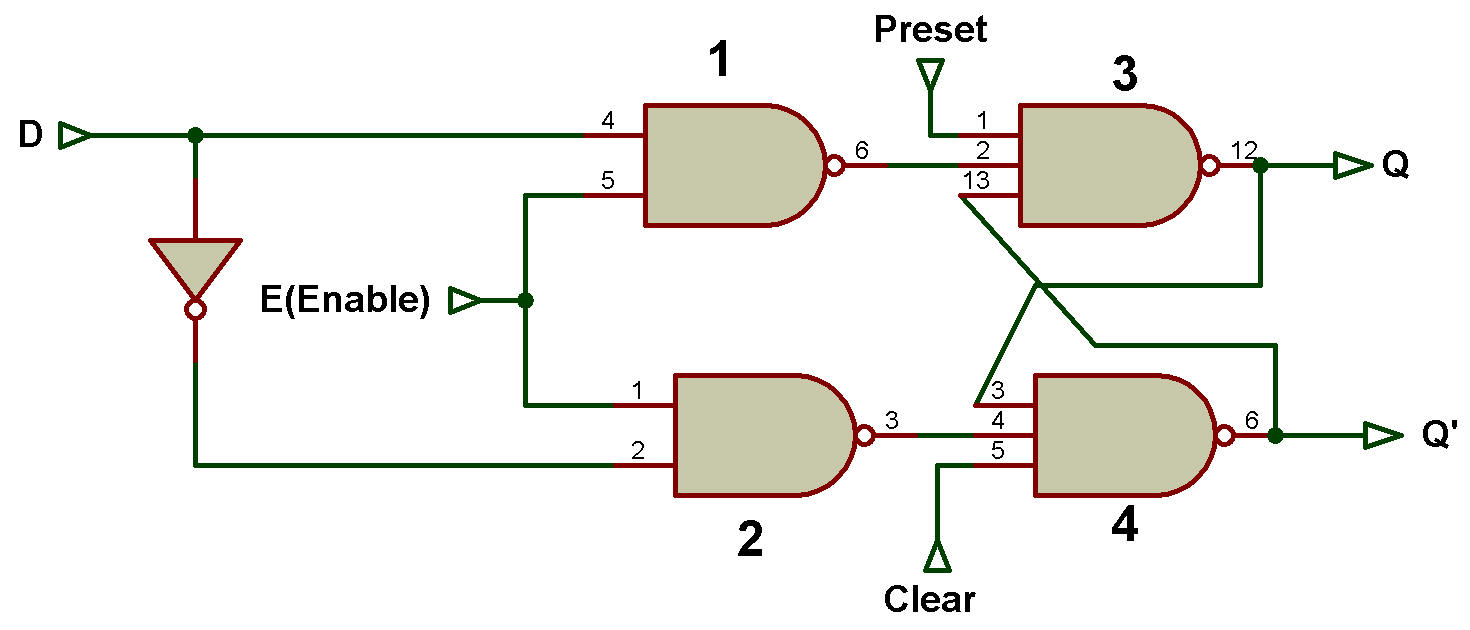

D Latch avec activation (E) (D Latch à porte)

Le D Latch avec entrée d'activation (E) ou entrée de commande est illustré à la figure ci-dessous et sa table de vérité est illustrée au tableau ci-dessous. Ce Latch est également appelé Latch à porte.

| E | D | Q | Q' |

| 0 | x | Q | Q' |

| 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

Lorsque l'entrée Enable (E) = 0, le Latch est désactivé et donc la sortie Q conserve sa dernière valeur quelle que soit la valeur d'entrée D, c'est-à-dire que Q' ne change pas si E = 0.

Lorsque E = 1, le Latch est activé et affiche Q = 1 si D = 1 ou sinon Q = 0 si D = 0.

Les entrées PRESET et CLEAR sont également illustrées dans la figure. Les entrées PRESET et CLEAR sont les entrées asynchrones utilisées pour amener la bascule à un état initial SET ou CLEAR.

Lorsque PRESET est activé, Q devient 1. Lorsque CLEAR est activé Q' = 1 et Q = 0.