Registres

Voir aussi : 74HC595

Les registres sont des dispositifs de stockage de données utilisés pour stocker 'n' bits d'informations binaires dans un groupe de bascules en cascade.

Ainsi, tout registre capable de stocker 'n' bits est constitué de 'n' bascules en cascade qui stockent 'n' bit d’informations binaires.

Notez que chaque bascule est capable de stocker 1 bit d'information, donc pour le stockage des bits 'n', des bascules 'n' sont nécessaires.

Les registres sont l’un des éléments constitutifs importants des circuits séquentiels.

Registres à décalage :

Si la sortie d'une bascule est connectée à l'entrée de la bascule suivante en cascade, ce circuit est appelé registre à décalage.

Toutes les bascules en cascade reçoivent la même impulsion d'horloge et donc SET et RESET simultanément.

Après chaque impulsion d'horloge, les données sont décalées d'un bit vers la gauche, vers la droite ou dans les deux sens, selon le circuit de connexion.

Selon le type de direction de déplacement des données, les registres à décalage sont classés comme suit :

i. Registre à décalage droit : dans le registre à décalage droit, les données sont décalées de gauche à droite.

ii. Registre à décalage gauche : dans le registre à décalage gauche, les données sont décalées de droite à gauche.

iii. Registre à décalage bidirectionnel : dans le registre à décalage bidirectionnel, les données peuvent être décalées vers la gauche ou vers la droite en fonction du signal de commande.

En fonction de la manière dont les données d'entrée sont appliquées (sous forme série ou sous forme parallèle) pour l'enregistrement et de la manière dont les données de sortie sont reçues (sous forme série ou forme parallèle), les registres à décalage sont classés dans les quatre types suivants :

• Registre à décalage d'entrée et de sortie en série (SISO)

• Registre à décalage d'entrée en série et en sortie parallèle (SIPO)

• Registre à décalage d'entrée en parallèle de sortie en série (PISO)

• Registre à décalage d'entrée et de sortie en parallèle (PIPO)

Discutons de chacun d'eux un par un.

Registre à décalage d'entrée et de sortie en série (SISO Serial In Serial Out)

Le registre à décalage Serial In Serial Out (SISO) accepte les données sous forme série et génère une sortie sous forme série.

Cela signifie une seule ligne pour l'entrée et une seule ligne pour la sortie afin que les données soient saisies bit par bit et reçues bit par bit.

Dans le registre à décalage SISO, les données peuvent être décalées vers la gauche ou vers la droite.

Les figures ci-dessous montrent respectivement le registre SISO à décalage vers la droite et le registre SISO à décalage vers la gauche.

SISO à décalage vers la droite

| Serial In → | → | → | → | → | Serial Out → |

SISO à décalage vers la gauche

| Serial Out ← | ← | ← | ← | ← | Serial In ← |

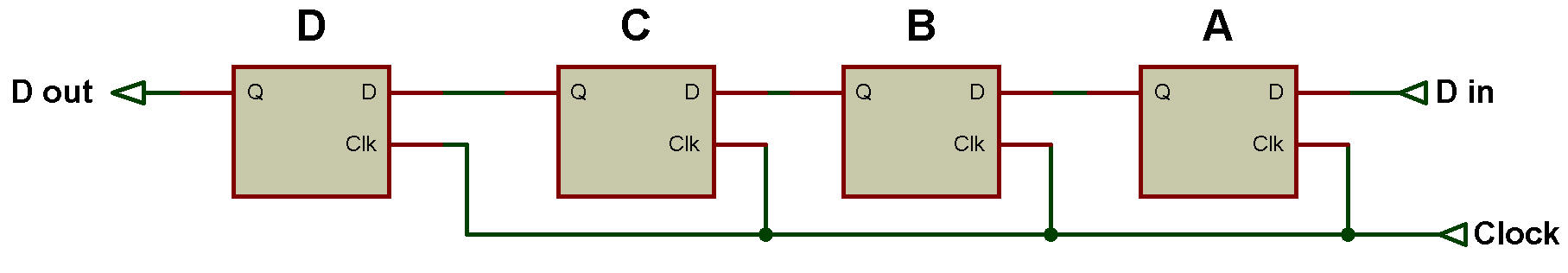

L'implémentation (schéma logique) du registre SISO utilisant la bascule 'D' est illustrée dans la figure ci-dessous:

Comme le montre la figure, il y a 4 bascules « D » connectées en cascade.

Din est l'entrée de la 1ère bascule et Dout est la sortie de la dernière bascule.

La sortie Q1 de la première bascule est connectée à l'entrée D2 de la deuxième bascule.

De même, la sortie Q2 de la deuxième bascule est connectée à l'entrée D3 de la troisième bascule et ainsi de suite.

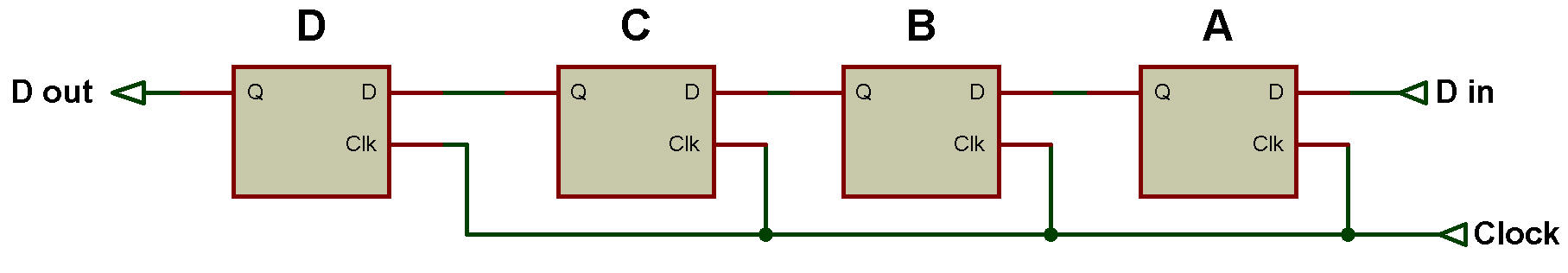

Comprenons maintenant le fonctionnement de la figure ci-dessous:

| Q4 | Q3 | Q2 | Q1 | ||||||

| ↓ | ←0 | ↓ | ←0 | ↓ | ←1 | ↓ | ←0 | ↓ | ←1 Din |

| Dout ←0 | 0 |

|

1 | 0 | 1 |

Supposons que, initialement la valeur de Q4Q3Q2Q1= 0010 et soit Din= 1

Ainsi, après la première impulsion d'horloge, les bits sont décalés vers la gauche d'une position de 1 bit.

Laissez maintenant Din = 0, puis après la 2ème impulsion d'horloge, les bits sont décalés vers la gauche d'une position de 1 bit.

| Q4 | Q3 | Q2 | Q1 | ||||||

| ↓ | ←0 | ↓ | ←1 | ↓ | ←0 | ↓ | ←1 | ↓ | ←0 Din |

| Dout ←0 | 1 |

|

0 | 1 | 0 |

De même, le cycle continue.

Le travail avec différentes valeurs de Din est présenté dans la figure ci-dessous:

Registre à décalage d'entrée en série et en sortie parallèle (SIPO)

Le registre à décalage Serial In Parallel Out (SIPO) accepte les données sous forme série et génère une sortie sous forme parallèle, comme le montre la figure ci-dessous:

| Parallel Out | |||||

| ↑ | ↑ | ↑ | ↑ | ↑ | |

| Serial In → | |||||

Ici, les données sont entrées bit par bit en série et une fois que les données complètes entrent dans les registres (en décalant un bit par bit), la sortie peut être obtenue sous forme parallèle, c'est-à-dire que les données complètes sont disponibles en même temps au lieu d'une petit à petit.

Le registre à décalage SIPO peut être décalé vers la droite ou vers la gauche. La figure montre le registre à décalage droit SIPO.

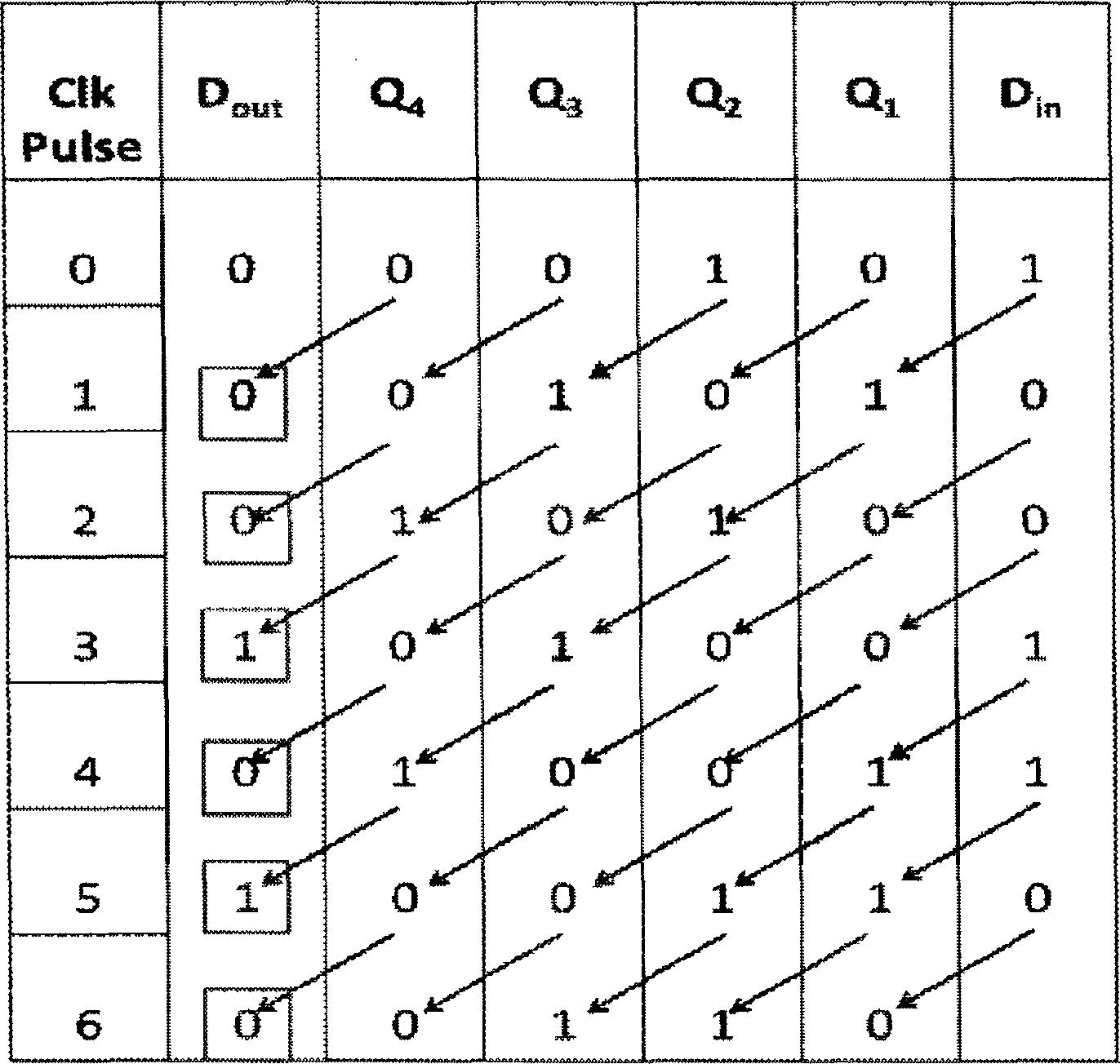

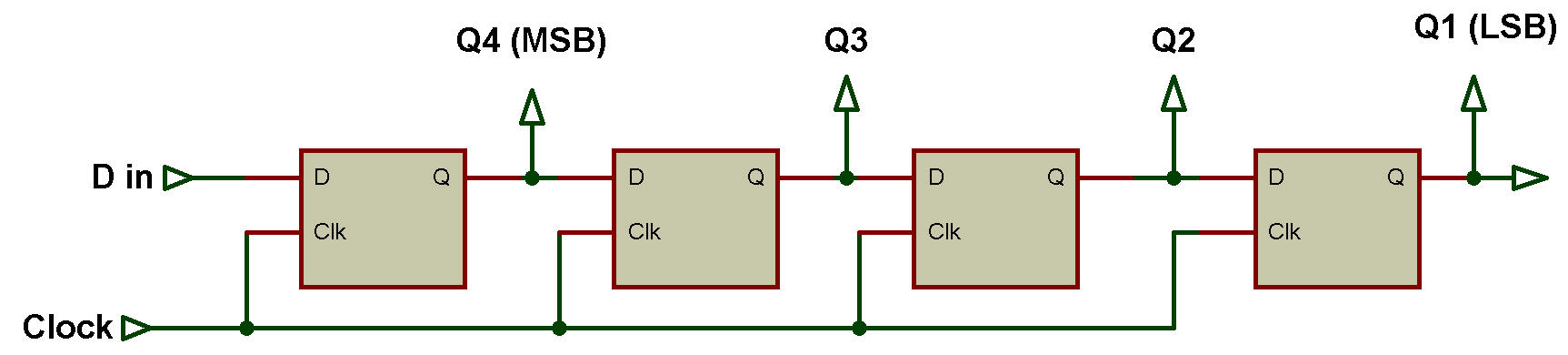

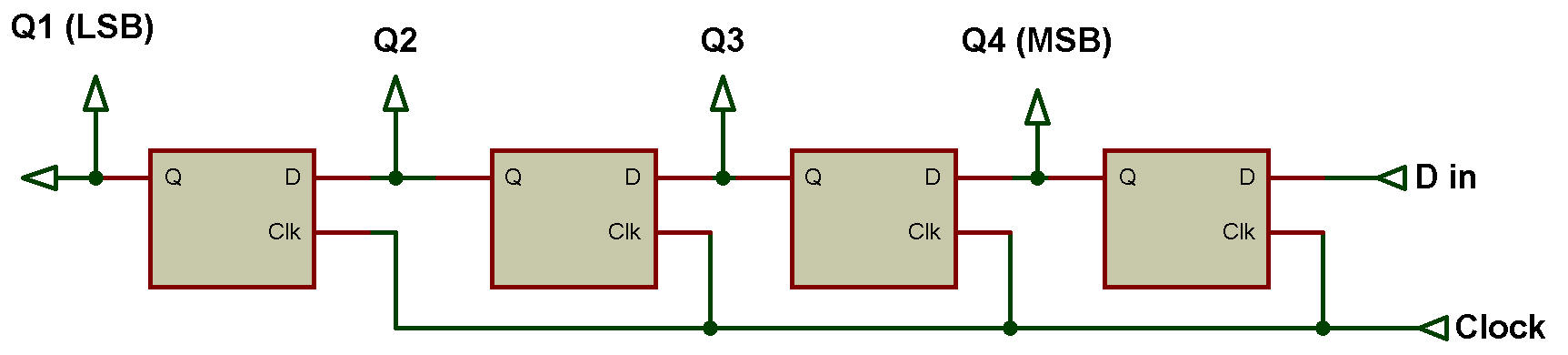

L'implémentation du registre SIPO utilisant la bascule D est illustrée dans la figure ci-dessous:

Comme le montre la figure, il y a quatre bascules « D » connectées en cascade.

Din est entré dans la quatrième bascule. Notez que dans le registre à décalage SIPO (décalage à droite), le LSB (Least Significant Bit) est d'abord entré en série dans l'entrée D4 de la dernière bascule.

La sortie Q4 est connectée à l'entrée D3 et ainsi de suite.

Comprenons le fonctionnement du registre à décalage SIPO (décalage à droite).

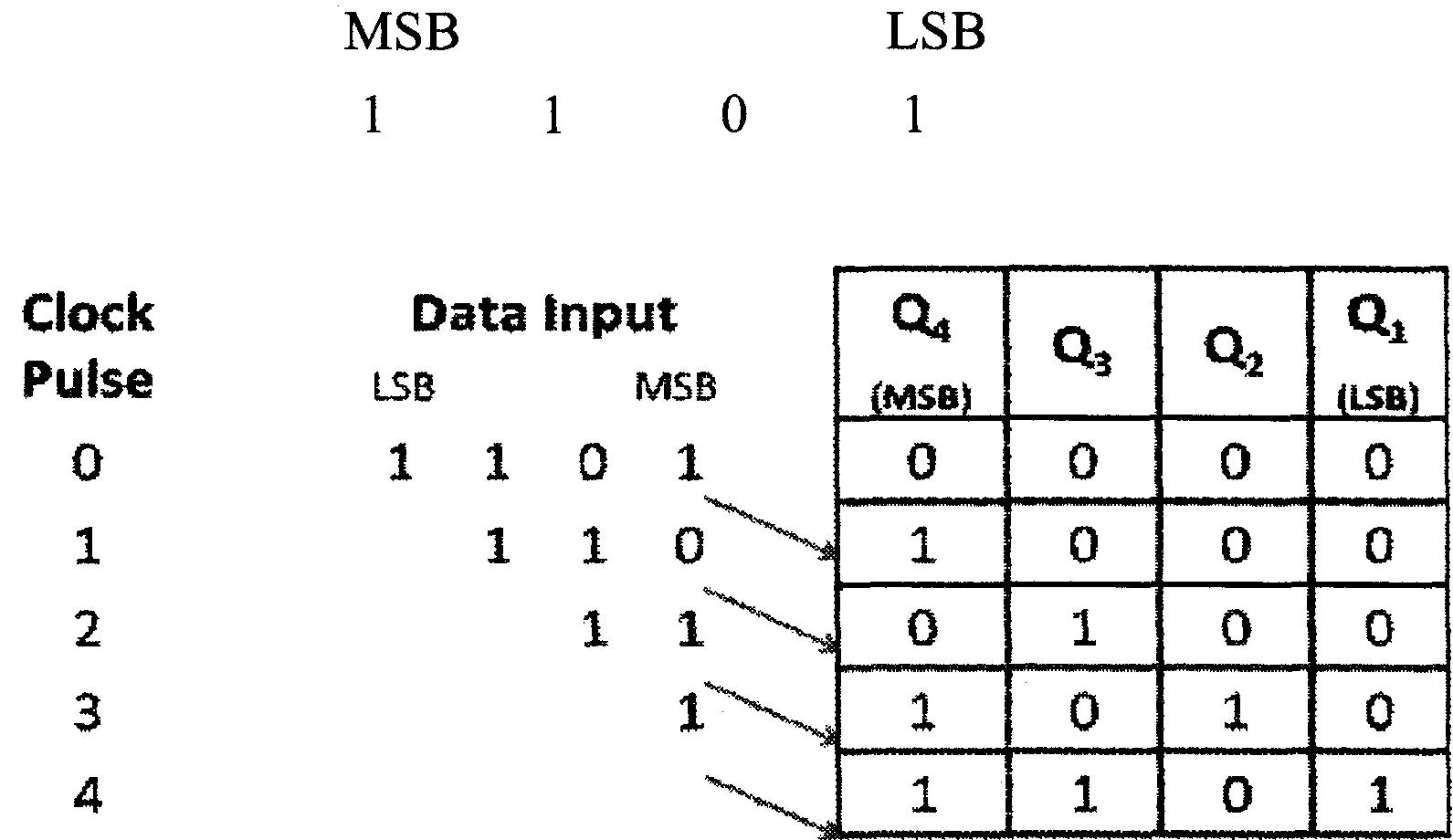

Ceci est illustré à la figure ci-dessous:

Supposons qu'initialement la valeur de Q4Q3Q2Q1= 0000 et les données à saisir en série soient 1101.

Comprenons le fonctionnement du registre à décalage SIPO (décalage à gauche).

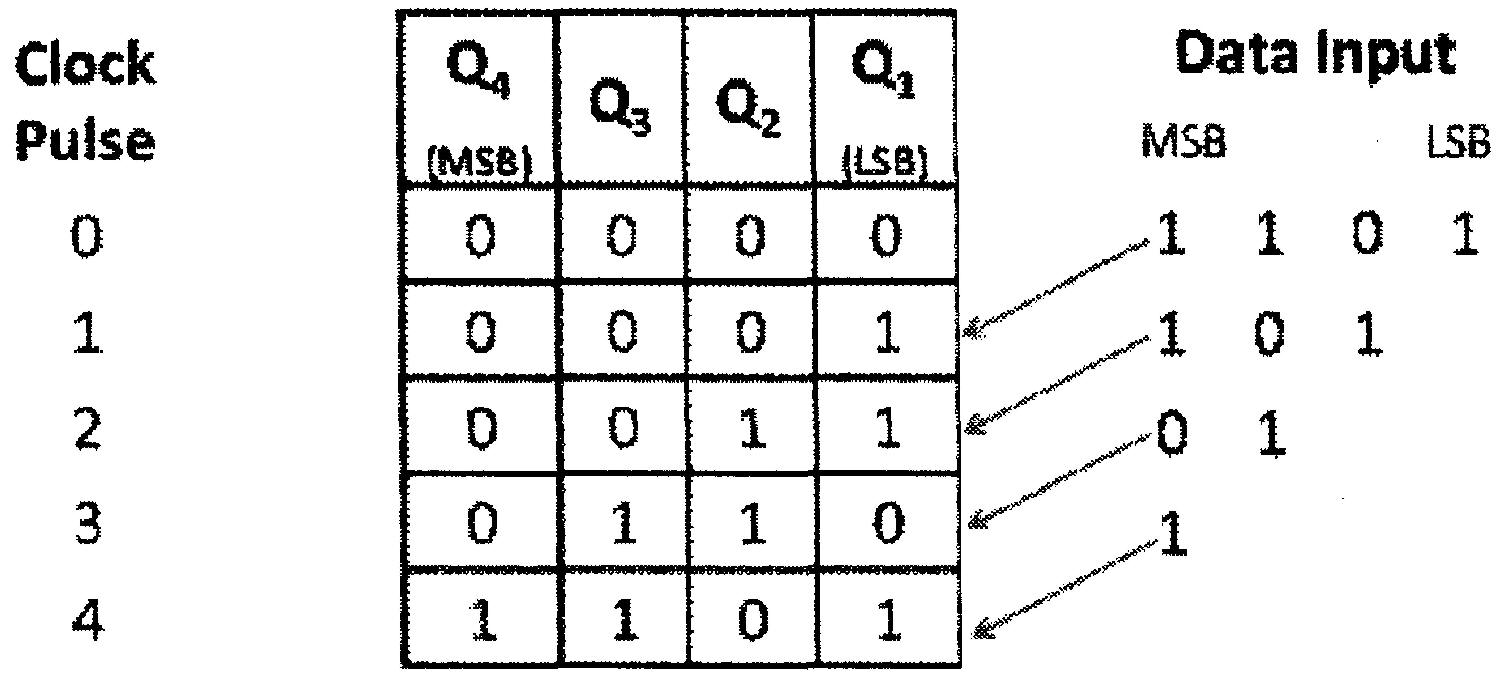

Ceci est illustré à la figure ci-dessous:

![]()

Supposons qu'initialement la valeur de Q4Q3Q2Q1= 0000 et que les données à saisir en série soient 1101.

Comme le montre la figure ci-dessous, le registre à décalage SIPO (décalage à gauche) MSB (bit le plus significatif également appelé bit de poids fort).

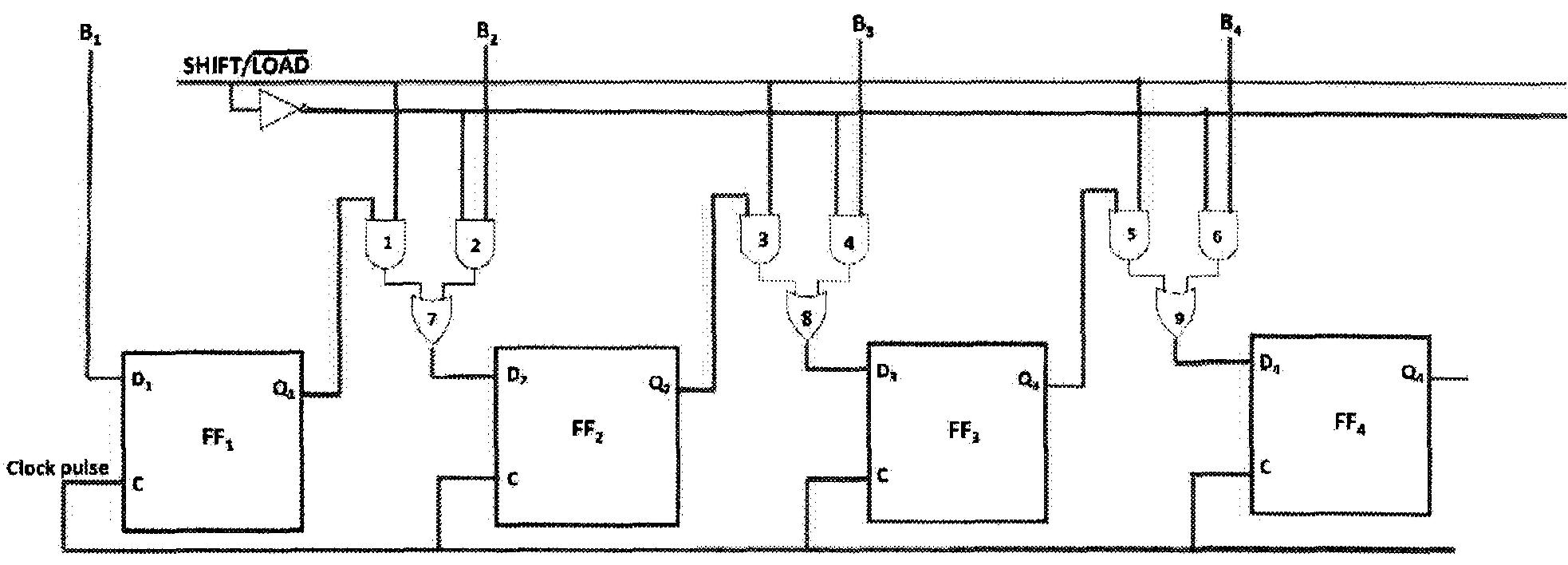

Le schéma logique du registre à décalage PISO est présenté dans la figure ci-dessous:

Comme le montre la figure, il existe deux modes ou nous pouvons dire qu'il existe deux états dans lesquels le circuit fonctionne.

Ces deux modes/états sont : SHIFT et LOAD.

Lorsque la ligne d'entrée SHIFT/LOAD est basse (0), les portes AND 2, 4 et 6 reçoivent une entrée haute (1) et elles deviennent actives et les bits de données binaires B1, B2, B3, B4 sont chargés en parallèle dans la bascule respective. (les données sont chargées sous forme parallèle vers l'entrée D1 de FF, D2 de FF2, D3 de FF3 et D4 de FF4).

Ainsi, lorsque la ligne d'entrée SHIFT/LOAD est LOW (0), il s'agit du mode LOAD pour le registre à décalage PISO.

Lorsque la ligne d'entrée SHIFT/LOAD est HIGH (1), les portes AND 2, 4 et 5 sont inactives et il n'y a donc pas de chargement de données mais les portes AND 1, 3 et 5 deviennent actives et donc les bits de données se déplacent de gauche à droite.

Ainsi, la sortie Q1 de FF1 se déplace vers la droite vers Q2 de FF2, Q2 est décalé vers Q3, Q3 est décalé vers Q4 et Q4 sort via Data Out.

De même, lorsque SHIFT/LOAD est HIGH, un changement de vitesse a lieu et ainsi de suite.

Ainsi, lorsque SHIFT/LOAD est HIGH, c'est le mode SHIFT.

Registre à décalage d'entrée et de sortie en parallèle (PIPO)

Le registre à décalage PIPO accepte les données sous forme parallèle et génère une sortie sous forme parallèle.

Cela signifie que tous les bits de données sont entrés simultanément dans leur bascule respective et que tous les bits de sortie sont reçus simultanément au lieu de bit par bit.

La figure ci-dessous montre le registre à décalage PIPO.

| Parallel In | |||

| ↓ | ↓ | ↓ | ↓ |

| 1 | 0 | 1 | 1 |

| ↓ | ↓ | ↓ | ↓ |

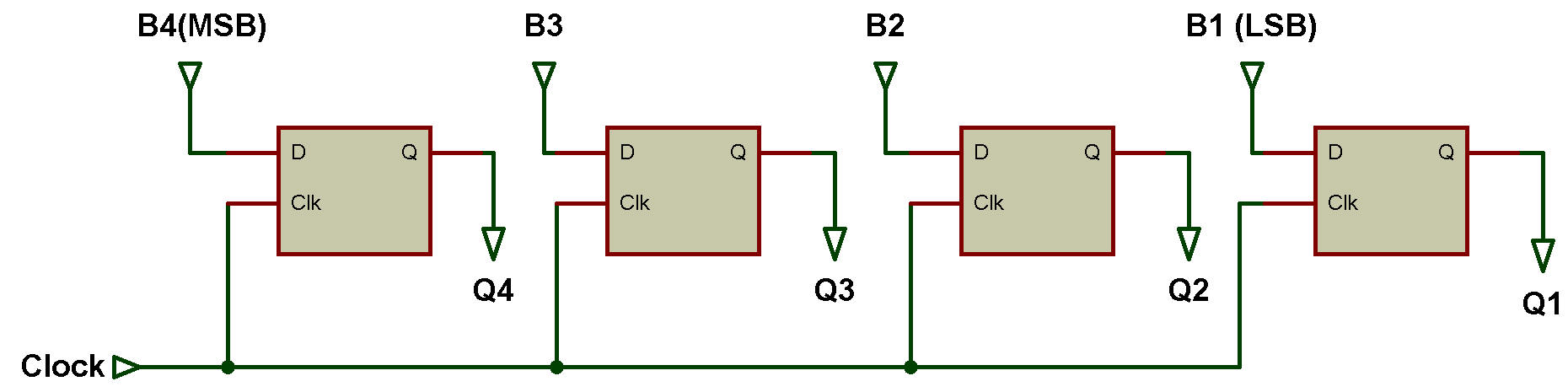

Le schéma logique est présenté dans la figure ci-dessous:

Le fonctionnement du registre à décalage PIPO est très simple.

Les bits B, B2, B3 et B4 des données binaires sont appliqués aux entrées respectives des bascules D1, D2, D3 et D4 et à l'entrée d'impulsion d'horloge suivante B4, B3, B2 et B1 apparaît la sortie de la bascule Q4, Q3, Q2 et Q1 respectivement.