NON-ET Une porte Universelle

NAND a universal gate

Les portes Logiques / Logic gates

Logique Résistance-transistor (RTL) / Resistor-Transistor Logic (RTL)

NON-OU Une porte Universelle

NOR a universal gate

Les circuits logiques / Logics (Digitals) circuits

| Breadboard | Portes logiques - Variantes | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Porte NON avec une Porte NON-ET NOT gate with a NAND gate |

Porte OU avec une Porte NON-ET OR gate with a NAND gate |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Porte ET avec une Porte NON-ET AND gate with a NAND gate |

Porte NON-OU avec une Porte NON-ET NOR gate with a NAND gate |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Porte XOR avec une Porte NON-ET XOR gate with a NAND gate |

Porte XNOR avec une Porte NON-ET XNOR gate with a NAND gate |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Portes Logiques Table de Vérité Logic Gates Truth Table |

Condensateur /

Résistance Capacitor / Resistor |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

NON-OU Une porte Universelle NOR a universal gate |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Nombres binaires dans l'électronique numérique Le système de numérotation binaire est un système de numérotation en base 2 qui suit les mêmes règles mathématiques que dans le système de numérotation décimal ou en base 10. Au lieu de puissances, par exemple 1,10,100, 1000, 10000, etc., les nombres binaires utilisent souvent des puissances de deux, ce qui double la valeur de chaque bit successif au fur et à mesure qu'il va plus loin, par exemple 1, 2,4, 8,16, 32, etc. Le nombre binaire est le fondement de la représentation de l’information dans un monde numérique, et les nombres binaires sont également appelés nombres de base 2. Les circuits électroniques numériques traitent les signaux contenant seulement deux états logiques (niveaux de tension), appelés Logique 0 et Logique 1. Un Logique 1 représente un niveau de tension plus élevé, par exemple +5 Volts, appelé valeur HAUTE, et un « Logique 0 » représente un niveau de tension inférieur, par exemple 0 Volt, appelé valeur FAIBLE. Les deux niveaux de tension dans l'électronique numérique sont appelés chiffres binaires (BITS), et les tensions utilisées pour représenter un circuit numérique peuvent être n'importe quelle tension comprise entre 0 Volt et 15 Volts, selon la technologie de fabrication utilisée pour fabriquer des circuits intégrés et des composants numériques. |

Binary Numbers in Digital

Electronics The binary number system is a Base-2 numbering system that follows the same mathematics rules as in the decimal or Base-10 number system. Instead of powers often, for example, 1,10,100, 1000, 10000, and so on, binary numbers use powers of two, which is doubling the value of each successive bit as it goes further, for example, 1, 2,4, 8,16, 32, etc. The binary number is the foundation of information representation in a digital world, and binary numbers are also known as Base 2 numbers. Digital electronic circuits process the signals containing only two logic states (voltage levels), known as Logic 0 and Logic 1. A Logic 1 represents a higher voltage level, to mention +5 Volts, referred to as a HIGH value, and A 'Logic 0' represents a lower voltage level, to mention 0 Volts, referred to as a LOW value. The two voltage levels in digital electronics are referred to as binary digiTS (BITS), and the voltages used to represent a digital circuit can be any voltage between 0 Volts to 15 Volts, depending on the fabrication technology used to manufacture digital ICs and digital components. |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

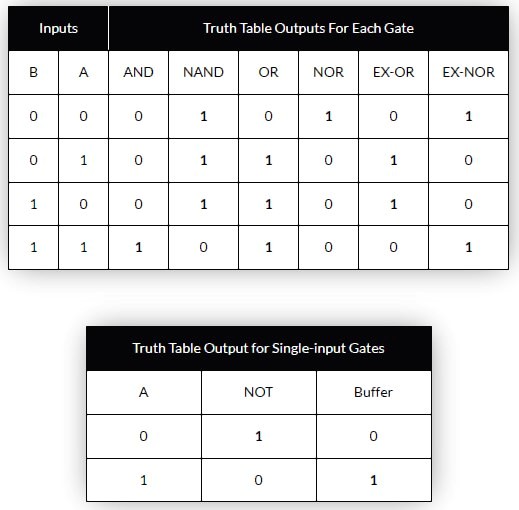

Introduction aux portes logiques numériques Les portes logiques sont des dispositifs semi-conducteurs et elles sont utilisées comme élément de base de tout appareil numérique. Une porte logique a deux entrées binaires ou plus A, B, C, etc., et une sortie binaire (Z), et sur l'entrée, nous fournissons des signaux numériques et sur la sortie, elle fournit une sortie numérique traitée. Le circuit intégré numérique (CI) se compose de portes logiques fabriquées à l'aide de transistors, comptant de quelques transistors à des millions de transistors en fonction des fonctions du CI. Les circuits intégrés ou CI sont regroupés en familles en fonction du nombre de portes ou de transistors dont ils disposent. Un exemple est qu'une simple porte NON n'a que quelques transistors, un microcontrôleur et un microprocesseur plus complexes ont quelques milliers de portes de transistors individuelles. Les dispositifs tels que les microcontrôleurs, les microprocesseurs et les circuits électroniques numériques sont conçus et construits à l'aide de portes logiques. Les portes logiques numériques de base effectuent des opérations logiques AND, OR et NOT sur des nombres binaires. Seuls deux niveaux ou états de tension sont autorisés dans la conception logique numérique, et ces deux états sont appelés Logique "0" et Logique "1", ou VRAI et FAUX ou HAUT et BAS, et deux états sont représentés dans les tables de vérité et l'algèbre booléenne, en utilisant respectivement les chiffres binaires « 0 » et « 1 ». Un simple interrupteur d'éclairage est un exemple d'état numérique, l'interrupteur peut être soit "OFF" soit "ON", dans un état ou dans l'autre, mais pas les deux états en même temps. La plupart des portes logiques numériques utilisent une « logique positive », c'est-à-dire qu'un niveau logique « BAS » ou « 0 » est représenté par une tension nulle (0 Volts ou masse), et un niveau logique « ÉLEVÉ » ou « 1 » est représenté. par une tension positive. La commutation d'un niveau de tension à l'autre niveau de tension, soit d'un niveau logique « 0 » à un « 1 » ou d'un « 1 » à un « 0 », doit être aussi rapide que possible pour éviter un fonctionnement défectueux du circuit logique. |

Introduction to Digital Logic

Gates Logic gates are semiconductor devices, and they are used as the building block of any digital device. A logic gate has two or more binary inputs A, B, C, and so on, and one binary output (Z), and on the input, we supply digital signals and on the output, it provides processed digital output. Digital Integrated Circuit (IC) consists of logic gates that are fabricated using transistors, counting a few transistors to millions of transistors depending upon functions of the IC. Integrated Circuits or ICs are grouped together into families according to the number of gates or transistors they have. An example is a simple NOT gate have only a few transistors, a more complex microcontroller and microprocessor have a few thousand individual transistor gates. Devices such as microcontrollers, microprocessors, and digital electronic circuits are designed and constructed using logic gates. The basic digital logic gates perform logical operations of AND, OR, and NOT on binary numbers. Only two voltage levels or states are allowed in digital logic design, and these two states are referred Logic "0" and, Logic "1", or TRUE and FALSE or HIGH and LOW, and two states are represented in truth tables and Boolean algebra by using the binary digits "0" and "1" respectively. A simple light switch is an example of a digital state, the switch can be either "OFF" or "ON", in one state or the other state, but not both states at the same time. Most of the digital logic gates use "Positive logic", that is a logic level "LOW" or "0" is represented by a zero voltage (0 Volts or ground), and a logic level "HIGH" or "1" is represented by a positive voltage. Switching from one voltage level to the other voltage level that is either from a logic level "0" to a "1" or a "1" to a "0" should be as fast as possible to prevent faulty operation of the logic circuit. |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Portes logiques universelles Une porte universelle peut être utilisée pour implémenter n'importe quelle fonction booléenne sans utiliser d'autres types de portes logiques, c'est-à-dire que n'importe quelle fonction booléenne peut être implémentée en utilisant uniquement des portes NAND et NOR. Charles Sanders Peirce (année 880-1881) a prouvé que les portes NAND seules ou les portes NOR seules peuvent être utilisées pour reproduire les fonctions de toutes les autres portes logiques. Pour une raison quelconque, son travail n'a été publié qu'en 1933, et le premier qui a publié la preuve en était par Henry M. Sheffer en 1913. Bien que nous utilisions la porte NAND comme porte universelle tout au long de cette section, seule la porte NAND est discutée en détail ici. Porte NAND La porte NAND (NON ET) n'est rien d'autre qu'une porte ET suivie d'une porte NON, c'est-à-dire que la sortie de la porte ET est connectée à l'entrée de la porte NON. La NAND est également connue sous le nom de porte universelle car en utilisant des portes NAND, il est possible de construire d'autres portes logiques. Les sorties de toutes les portes NAND sont à 1 logique si l'une des entrées passe à 0 logique. Si les deux entrées sont à 1 logique, alors la sortie de la porte NAND est à 0 logique. |

Universal Logic Gates A universal gate can be used to implement any Boolean function without using any other types of logic gate, that is any Boolean function can be implemented using only NAND and NOR gates. Charles Sanders Peirce (year 880-1881) proved that NAND gates alone or NOR gates alone can be used to reproduce the functions of all the other logic gates. For some reason, his work was not published until the year 1933, and the first published proof was by Henry M. Sheffer in 1913. Though we are using the NAND gate as a universal gate throughout this section, only NAND gate is in detail discussed here. NAND Gate The NAND (NOT AND) gate is nothing but an AND gate followed by a NOT gate, that is the output of AND gate is connected to the input of the NOT gate. The NAND is also known as the Universal Gate because by using NAND gates it is possible to construct other logic gates. The outputs of all NAND gates are logic 1 if any of the inputs goes logic 0. If both inputs are logic 1, then the output of the NAND gate is logic 0. |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

1 = A, 2 = B, 3 = Z  |

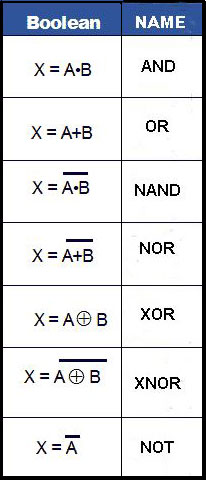

Table de vérité / Truth Tables

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Le fonctionnement d'une porte NAND logique numérique à deux entrées est défini comme « Si A ou B n'est PAS vrai, alors Z est vrai ». | The operation of a two-input digital logic NAND gate is defined as "If either A or B is NOT true, then Z is true". | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

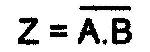

Tables de vérité La table de vérité est un tableau mathématique qui représente l'expression booléenne d'une fonction de porte logique qui montre toutes les combinaisons d'entrée possibles de variables logiques dans la porte logique, ainsi que le niveau logique de sortie en fonction de la combinaison de ces entrées. Chaque variable logique d'entrée possède une colonne dans la table de vérité et une colonne de sortie affichant les résultats possibles de l'opération logique. Un exemple consiste à considérer une porte logique à deux entrées avec des variables d'entrée nommées A et B, et quatre combinaisons d'entrées sont possibles, comme indiqué dans la table de vérité. La colonne de sortie de la table de vérité affiche les niveaux logiques en fonction des fonctions logiques d'entrée. Chaque ligne de la table de vérité représente toutes les entrées possibles du circuit de porte logique et les sorties correspondantes. |

Truth Tables Truth Table is a mathematical table that represents the Boolean expression of a logic gate function which shows all possible input combinations of logical variables to the logic gate, and the output logic level depending upon the combination of these input(s). Each input logical variable has a column in the truth table, and an output column showing possible results of the logical operation. One example is considering a two-input logic gate with input variables named A and B, and there are four input combinations that are possible which are as shown truth table. The output column of the truth table shows the logic levels depending on the input logic functions. Each row of the truth table represents all possible inputs to the logic gate circuit and the corresponding outputs. |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Variantes 74XXIC Les circuits intégrés de la série 74XX sont disponibles dans les technologies TTL et CMOS, et voici quelques exemples de circuits intégrés répertoriés ci-dessous. - 7408 (Standard TTL, Quad 2 entrées ET portes) - 74N08 (Standard TTL, Quad 2 entrées ET portes) - 74LS08 (Schottky basse consommation, portes ET Quad 2 entrées) - 74HC08 (CMOS haute vitesse avec entrées compatibles CMOS Quad 2 entrées ET portes) - 74HCT08 (CMOS haute vitesse avec entrées compatibles CMOS, Quad 2 entrées, portes ET)... La tension d'alimentation CC (Vcc) de la série 74XX doit être fournie dans la limite de +4,75 Volts à +5,25 Volts. Chaque variante du IC 74XX fonctionne sur une tension d'alimentation CC (Vcc) différente, bien que toutes les variantes du IC 74XX fonctionnent sur une alimentation CC de + 5 Volts, pour tous les types de vérification de portes logiques, vous pouvez utiliser n'importe quelle variante du IC, cela fonctionne ! |

74XXIC Variants 74XX series IC is available in TTL and CMOS technologies, and here are some IC examples listed below. - 7408 (Standard TTL, Quad 2-input AND gates) - 74N08 (Standard TTL, Quad 2-input AND gates) - 74LS08 (Low-power Schottky, Quad 2-input AND gates) - 74HC08 (High-speed CMOS with CMOS compatible inputs Quad 2-input AND gates) - 74HCT08 (High-speed CMOS with CMOS compatible inputs, Quad 2-input, AND gates) ... The DC power supply voltage (Vcc) for the 74XX series should be supplied within the limit of +4.75 Volts to +5.25 Volts. Each variant of 74XX IC works on a different DC power supply voltage (Vcc), though all 74XX IC variant works on + 5 Volts DC power supply, for all types of logic gates verification you can use any of the IC variants, it works! |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Circuits intégrés numériques TTL série 74LS LS signifie Low-power Schottky, la société de fabrication de dispositifs à semi-conducteurs Texas Instruments a introduit la famille de circuits intégrés (IC) TTL, et TTL signifie Transistor-Transistor Logic, et le circuit intégré TTL utilise deux transistors pour piloter les sorties. Un transistor pour abaisser la sortie à un niveau bas et un transistor pour amener la sortie à un niveau haut. Schottky est le terme qui fait référence à une technologie permettant de fabriquer des transistors plus rapides, et les circuits intégrés de la famille TTL sont disponibles auprès de différents fabricants. Le physicien allemand Walter Hans Schottky a développé la diode semi-conductrice formée par la jonction d'un semi-conducteur avec un métal. La tension directe de Schottky est comprise entre 150 millivolts et 450 millivolts, et cette exigence de tension directe inférieure de la diode permet des vitesses de commutation plus élevées et une meilleure efficacité. La diode Schottky est également appelée « diode barrière Schottky » ou « diode porteuse chaude ». La famille logique de circuits intégrés Schottky Transistor-Transistor-Logic (tels que S et LS) utilise des diodes Schottky avec des transistors aux endroits critiques. Un circuit intégré fabriqué à partir d'un transistor Schottky est une combinaison d'un transistor et d'une diode Schottky qui empêche le transistor de saturer en détournant le courant d'entrée excessif. Ce transistor est également appelé transistor à serrage Schottky. Tous les fabricants de circuits intégrés TTL utilisent un système de dénomination commun, par exemple dans le circuit intégré SN74LS00 (deux portes Quad NAND d'entrée), le préfixe SN indique que le nom du fabricant est Texas Instruments. Tous les fabricants ont leurs propres codes de préfixe, mais si le reste du nom du circuit intégré correspond, le circuit intégré doit remplir exactement la même fonction que celle spécifiée. Le code numérique 74 indique que la puce est conforme aux exigences de l'industrie informatique civile, étant capable de fonctionner sur une plage de température de 0 degrés Celsius à 70 degrés Celsius, et le code 54 indique la plage de température de -55 degrés Celsius à 125 degrés celsius requis par les applications militaires et certaines applications industrielles. Les lettres LS indiquent la sous-famille du circuit intégré et les deux derniers chiffres 00 indiquent la fonction logique remplie par le circuit intégré. Les six sous-familles TTL sont présentées dans le tableau ci-dessous et chacune des six sous-familles offre des exigences de vitesse/puissance différentes. |

74LS Series TTL Digital Integrated Circuits LS stands for Low-power Schottky, the semiconductor devices manufacturing company Texas Instruments introduced the TTL family of integrated circuits (IC), and TTL stands for Transistor-Transistor Logic, and The TTL integrated circuit uses two transistors to drive the outputs. One transistor to pull the output down to a low level, and one transistor to pull the output up to a high level. Schottky is the term refers to a technology for making faster transistors, and the integrated circuits from the TTL family are available from various manufacturers. A German physicist Walter Hans Schottky developed the semiconductor diode formed by the junction of a semiconductor with a metal. Schottky's forward voltage is 150 milli Volts to 450 milli Volts, and this lower forward voltage requirement of the diode allows higher switching speeds and better efficiency. The Schottky diode is also referred as the Schottky barrier diode1 or 'hot-carrier diode. The Schottky Transistor-Transistor-Logic logic family of integrated circuits (such as S and LS) uses Schottky diodes with transistors in critical places. A Schottky transistor fabricated IC is a combination of a transistor and a Schottky diode that prevents the transistor from saturating by diverting the excessive input current, and this transistor is also called a Schottky-clamped transistor. All manufacturers of TTL integrated circuits use a common naming system, for example in the integrated circuit SN74LS00 (two input Quad NAND gates), the prefix SN indicates that the manufacturer's name is Texas Instruments. All manufacturers have their own prefix codes, but if the remainder of the integrated circuit name matches, the integrated circuit should perform exactly the same function as specified. The numeric code 74 indicates that the chip conforms to the requirements of the civilian computer industry, being able to operate over a temperature range of 0 degrees Celsius to 70 degrees Celsius, and code 54 indicates the temperature range of -55 degrees Celsius to 125 degree Celsius required by military and some industrial applications. The letters LS indicate the subfamily of the integrated circuit, and the last two digits 00 indicate the logical function performed by the integrated circuit. The six TTL subfamilies are shown in the table below, and each of the six subfamilies offers different speed/power requirements. |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Circuits intégrés numériques CMOS Le principal inconvénient de la série TTL est que les portes logiques sont conçues sur la technologie logique des transistors bipolaires (le BJT, le transistor à jonction bipolaire, est utilisé), et le BJT est un composant fonctionnant en fonction du courant et consomme une énorme quantité d'énergie provenant d'une alimentation de +5 volts. . Les grilles des transistors bipolaires TTL ont une limitation sur leur vitesse de fonctionnement lors de la commutation (délai de propagation) des niveaux logiques « 0 » à « 1 » et vice-versa. Pour surmonter les limitations du BJT, une autre technologie appelée « CMOS » (Complementary Metal Oxide Semiconductor) est utilisée pour fabriquer des portes logiques avec des transistors à effet de champ (FET). Les portes logiques CMOS utilisent à la fois des MOSFET à canal P et à canal N, et sans commutation et dans des conditions de repos, les portes CMOS consomment une énergie presque nulle (1 µA à 2 µA), ce qui rend les portes logiques CMOS adaptées aux circuits de batterie à faible consommation et avec Vitesses de commutation vers le haut de 100 MHz, ils sont utilisés dans les circuits de synchronisation et informatiques haute fréquence. Circuits intégrés CMOS série 4000 La famille logique de la série 4000 est un CMOS de circuits intégrés introduits en 1968 par Radio Corporation of America (RCA), et ils sont capables de fonctionner avec une plage de tension de 5 Volts CC à 20 Volts, la plage de tension de la série 4000 est supérieur à toute autre famille logique CMOS. La conception du circuit de la série 4000 est plus simple et présente une faible consommation d'énergie, peut fonctionner avec une large plage de tensions d'alimentation et présente une capacité de sortance (capacité de pilotage de charge) incroyablement accrue par rapport à la série TTL. Cette capacité de la série 4000 est la plus adaptée au prototypage de conceptions d'intégration à grande échelle (LSI). Tous les fabricants ont leurs propres codes de préfixe, mais si le reste du nom du circuit intégré correspond, le circuit intégré doit remplir exactement la même fonction que celle spécifiée. |

CMOS Digital Integrated Circuits The main drawback with the TTL series is logic gates are designed on bipolar transistor logic technology (BJT the Bipolar Junction Transistor are used), and BJT is a current-based operated component and consumes a huge amount of power from a +5 volts power supply. The TTL bipolar transistor gates have a limitation on their operating speed while switching (propagation delay) from logic levels "0" to "1" and vice-versa. To overcome BJT limitations, another technology called "CMOS" (Complementary Metal Oxide Semiconductor) is used to fabricate logic gates with Field Effect Transistors (FET) were implemented. CMOS logic gates use both P-channel and N-channel MOSFET are used, and with no switching and at quiescent conditions, CMOS gates consume nearly zero power (1 uA to 2uA) making CMOS logic gates suitable for low-power battery circuits and with 100 MHz upwards switching speeds they are used in high-frequency timing and computer circuits. 4000 series CMOS Integrated circuits The logic family of 4000 series is a CMOS of integrated circuits that were introduced in the year 1968 by the Radio Corporation of America (RCA), and they are capable of functioning with a voltage range of DC 5 Volts to 20 Volts, the voltage range of the 4000 series is higher than any other CMOS logic family. The 4000 series circuit design is simpler and has low power consumption, can function with a wide range of supply voltages, and has an incredibly increased fan-out (load-driving capability) capability compared to the TTL series. This ability of the 4000 series is most suitable for prototyping Large Scale Integration (LSI) designs. All manufacturers have their own prefix codes, but if the remainder of the integrated circuit name matches, the integrated circuit should perform exactly the same function as specified. |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

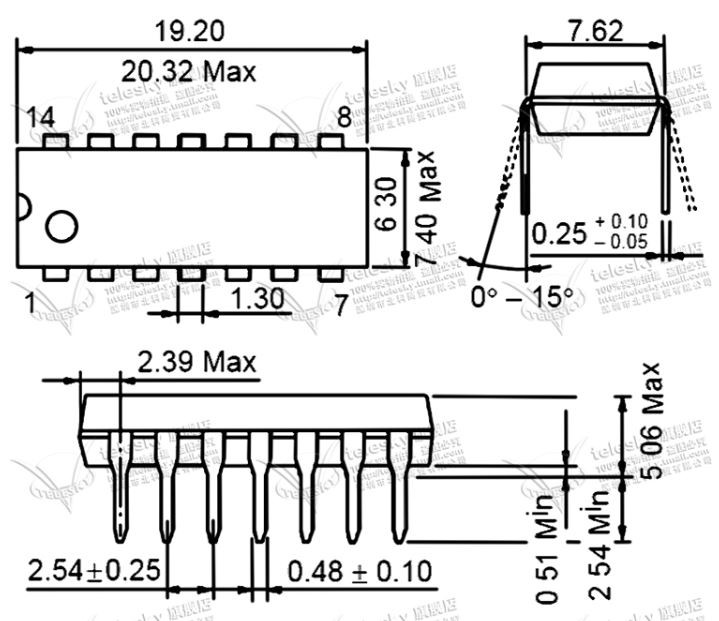

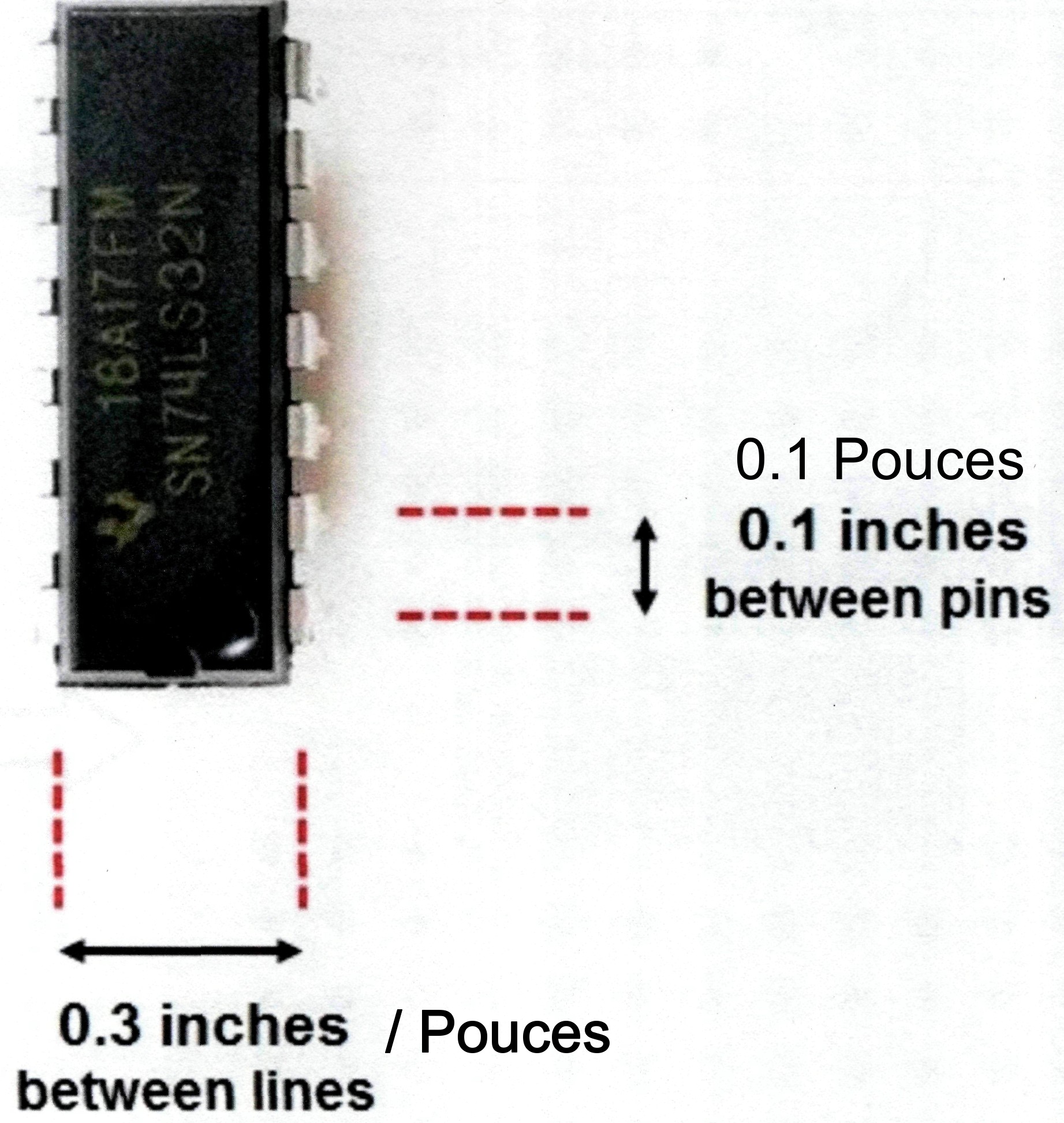

Circuits intégrés à boîtier DIL De nombreux circuits intégrés sont fabriqués dans un boîtier Dual in-Line, ou DIP (également appelé simplement Dual in-Line ou DIL), C'est-à-dire que le circuit intégré comporte deux rangées de broches parallèles, comme le montre l'image ci-dessous. Si le boîtier DIP du circuit intégré est fabriqué en plastique, il est alors appelé boîtier en plastique double en ligne (PDIP). |

DIL Package Integrated Circuits Many of the integrated circuits are manufactured in a Dual in-Line Package, or DIP (also referred to as just Dual in-Line or DIL). That is, the IC has two parallel rows of pins as shown in the image below. If the DIP package of IC is made with plastic, then it is called Plastic Dual in-Line Package (PDIP). |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Un ravin existe au milieu du breadboard et le ravin au milieu du

breadboard (entre les colonnes E et F) a la bonne largeur pour qu'un

CI puisse s'adapter, se trouve sur l'espace, avec un jeu de broches

dans la colonne E, et un jeu de broches dans la colonne F, comme

indiqué dans l'image ci-dessous. La distance entre deux trous sur le breadboard est de 0,1 pouce et la distance entre les rangées E et F est de 0,3 pouce. Le breadboard n'est pas adaptée à l'assemblage de composants montés en surface (SMC), et ces composants SMC ont des broches courtes et plates qui sont trop petites et sont conçues pour être soudées à la surface (pastilles) d'une carte de circuit imprimé (PCB), au lieu de à travers des trous. |

A ravine exists in the middle of the breadboard, and the ravine in

the middle of a breadboard (between Columns E and F) is the right

width for an IC to fit, sits on the gap, with one set of pins in

Column E, and one set of pins in Column F as shown in the image

below. The distance between two holes on the breadboard is 0.1 inches and the distance between E and F rows is 0.3 inches. The breadboard is not suitable for surface mount components (SMC) assembly, and these SMC components have short and flat pins which are too small and are designed to be soldered to the surface (pads) of a printed circuit board (PCB), instead of through holes. |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Numéros de broches Les broches sont numérotées dans le sens inverse des aiguilles d'une montre autour du CI (puce) en commençant près de l'encoche ou du point. Les schémas montrent la numérotation des circuits intégrés à 14 broches, mais le principe est le même pour toutes les tailles. |

Pin numbers The pins are numbered anti-clockwise around the IC (chip) starting near the notch or dot. The diagrams show the numbering for 14-pin ICs, but the principle is the same for all sizes. |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| IC 74LS00 Photos et Configuration des broches | IC 74LS00 Photo and Pin Configuration | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| IC 4011 Photos et Configuration des broches | IC 4011 Photo and Pin Configuration | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||